产品手册

仪器型号: \_\_\_\_P5551A

西安安泰测试科技有限公司 仪器维修|租赁|销售|测试

地址:西安市高新区纬二十六路 369 号电话: 400-876-5512网址: www.agitekservice.com座机: 029-88827159

### P5551A

#### PCI Express Protocol Exerciser for PCIe 5.0

#### Introduction

P5551A PCIe 5.0 Protocol Exerciser allows test engineers to emulate both PCIe root complex and endpoint devices when validating PCIe designs. The exerciser supports traffic generation from 2.5 GT/s through 32 GT/s and lane widths from x1 to x16. The tool includes over 100 built-in LTSSM test cases, error insertion capability at the TLP and DLLP layer, and an included protocol checker.

#### **Table of Contents**

| ntroduction                                                        | 1  |

|--------------------------------------------------------------------|----|

| Product Overview                                                   | 3  |

| Combined Exerciser and Analyzer Software                           | 4  |

| Backplane Test Platform                                            | 5  |

| Use Case: Root Complex Emulation for Testing Endpoints             | 6  |

| Use Case: PCIe End Point Emulation for Testing Root Complex        | 7  |

| Ready to Go Protocol Test Features                                 | 7  |

| LTSSM Tester                                                       | 8  |

| Link Configuration                                                 | 9  |

| Lane Configuration                                                 | 9  |

| Advanced Protocol Test Features                                    | 9  |

| Replay Function                                                    | 9  |

| Equalization and Transceiver Configuration                         | 10 |

| Skip OS Configuration                                              | 10 |

| Customized PCIe Traffic Generation                                 | 10 |

| Power Management Features                                          | 10 |

| Automation API                                                     | 11 |

| Product Specifications                                             | 11 |

| Additional Recommended Hardware                                    | 13 |

| Ordering Information                                               | 13 |

| Software Licensing and KeysightCare Software Support Subscriptions | 14 |

#### **Product Overview**

The Keysight P5551A PCIe 5.0 Protocol Exerciser provides test and validation engineers a powerful tool for vetting and debugging their PCIe designs. The P5551A uses an integrated, single add-in-card design which greatly simplifies the connection and setup of the tool while offering greatly improved signal integrity compared to other architectures. This enables test and validation engineers to focus their time and energy on designing and automating unique test cases for their products, rather than wasting time dealing with an overly complex test setup with poor signal integrity.

The foundation of the P5551A is the improved signal integrity provided through the integrated design of the Exerciser card which provides a solid, trustworthy test platform. This compact design allows Keysight engineers great versatility in ensuring that the P5551A would have signal integrity characteristics that could be configurable enough to be tuned for many different test environments, while also offering quick link up capability for test cases that focus on higher layer protocol debugging.

The P5551A Exerciser supports PCIe speeds from 2.5 GT/s up to 32 GT/s and Lane widths from x4, x8 and x16 along with the following features:

- Follows all PCle 5.0 electrical specifications.

- Automated link training to 32GT/s

- Ability to initiate Higher and Lower Speed Changes between 2.5GT/s to max supported speed.

- PCle 5.0 link training bypass supported

- Traffic generation directly from GUI or from automated user generated scripts.

- Lane Reversal and polarity detection

- · Scalable flow control supported

- Control of the Link Training and Status State Machine (LTSSM) operation

- Lane and Speed Negotiations from 2.5 GT/s to 32 GT/s.

- Real Time Equalization process

- Transaction Layer Generation (Memory Read/Write, IO Request, Config Request)

- Error Insertion via NAK, Completion Error, DLLP Errors

- Emulate either upstream (Root Complex) or downstream (Endpoint) ports

#### **Combined Exerciser and Analyzer Software**

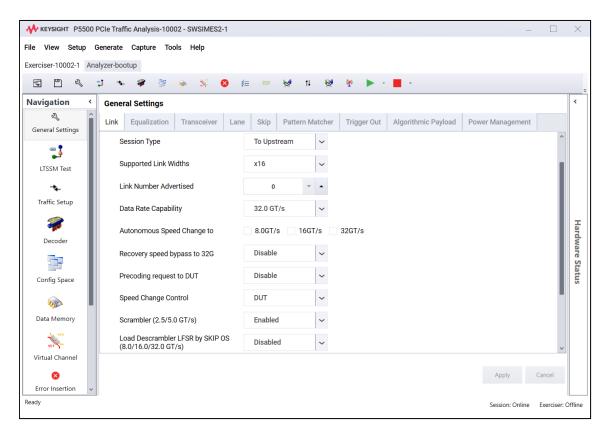

Both the Keysight P5551A PCle 5.0 Protocol Exerciser and its companion tool, the P5552A PCle 5.0 Analyzer, are supported by a single combined software interface, offering the user easy access to all of the powerful capabilities of both tools. Through a simple, tab based interface, the user can configure the Exerciser and Analyzer side by side with just a few clicks. The Exerciser GUI provides deep functionality for configuring Traffic Setup, while also providing improved data exchange with the analyzer.

Figure 1. Exerciser equalization configuration.

#### **Backplane Test Platform**

Even more test setups can be created using the P5551A Exerciser along with the Keysight P5563A PCIe 5.0 Protocol Backplane Test Platform. The P5563A Test Platform features SI enhancements to reduce crosstalk and improve signal integrity, where low-loss material in utilized in order to support reliable connections at 32 GT/s.

- CEM form factor for endpoint devices. Automated link training to 32 GT/s

- Integrated low noise power supply with Auxiliary PCIe power available for high power endpoint devices

- Stable mechanical construction for reliable operation during bring-up

- One pair of CEM slots for connecting the Exerciser with a DUT.

Figure 2. P5563A Test Backplane

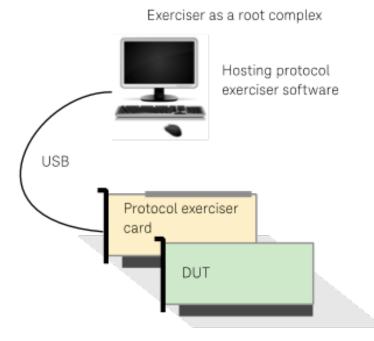

## **Use Case: Root Complex Emulation for Testing Endpoints**

The Keysight P5551A can be configured to emulate a PCle 5.0 root complex with its own link, equalization, and power management parameters.

When emulating a root complex, the P5551A cards can connect to a PCIe slot on the P5563A test backplane board with an endpoint (DUT) sitting in another PCIe slot. The exerciser then provides downstream stimulus to the DUT as a root complex just as a regular Host System would. The exerciser then can check the data received from the DUT for errors. This common configuration is simple to setup and easy for the end user to operate and troubleshoot.

Figure 3. The P5551A PCle 5.0 Protocol Exerciser can be used to emulate a Root Complex.

The P5552A PCIe 5.0 Protocol Analyzer can also be added to the above configuration to decode and analyze the traffic between the emulated root complex and end point DUT.

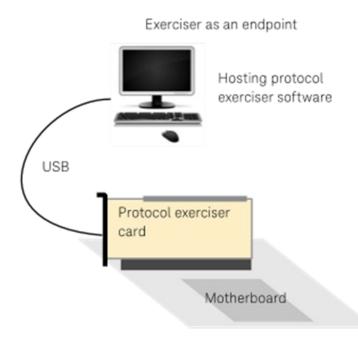

# **Use Case: PCIe End Point Emulation for Testing Root Complex**

When emulating an end point the PCIe exerciser card can be plugged into any PCIe slot on a system motherboard, similar to how any other PCIe add-in-card device, such as a NIC, Graphics Card, or SSD, would be plugged in.

Figure 4. The P5551A PCIe 5.0 Protocol Exerciser can be used to emulate a PCIe Endpoint.

The P5552A PCIe 5.0 Protocol Analyzer can also be added to the above configuration to decode and analyze the traffic between the system motherboard and the emulated end point.

#### Ready to Go Protocol Test Features

The P5551A is designed to be easy to setup, connect, and be quickly configured to bring up the PCIe link and check basic LTSSM and protocol functionality. To support this the P5551A has many features included that allow for quick validation of fundamental PCIe features.

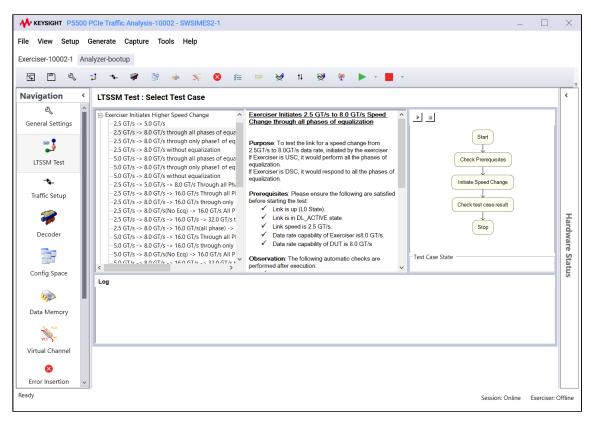

#### **LTSSM** Tester

Figure 5. Over 100 LTSSM test cases are included.

LTSSM Tester mode allows the user to validate the different paths through the branches of the Link Training Sequence State Machine that are defined for PCIe. With over 100 available LTSSM test cases, the exerciser can provide the user a clear picture of LTSSM compliance from 2.5 GT/s up to 32 GT/s. Test cases include checking for the following:

- · Equalization Failures

- Down Configuration and Up Configuration

- Current and Negotiated Data Rate failures while in Recovery

- · Redo Equalization Requests

- Framing Error insertion via Invalid Sync Bits

- Speed Change requests with Equalization skipped

#### **Link Configuration**

The P5551A PCIe 5.0 Exerciser supports a wide variety of configuration options for the PCIe link providing the user with a powerful tool for testing PCIe devices. The user has the ability configure the following parameters:

- Enable PCIe, SRIOV protocols.

- Emulate upstream or downstream port

- Lane widths of x1, x2, x4, x8, x16

- Data Rate support for 2.5 GT/s, 5 GT/s, 8 GT/s 16 GTs, 32 GT/s

- Autonomous Speed Change capability for 8 GT/s 16 GTs, 32 GT/s

#### **Lane Configuration**

The P5551A PCIe 5.0 Exerciser supports automatic lane reversal to be enabled and disabled, as well as the ability to invert transmitter lane polarity on specific lanes.

#### **Advanced Protocol Test Features**

While the P5551A is designed to be easy to setup and configure, many users will create customized, automated test configurations specific to their needs. The following section describes some of the indepth protocol test capability supported by the P5551A Exercisers that validation engineers can take advantage of in their own customized test setups.

#### **Replay Function**

Data captured by the P5552A PCIe analyzer can be replayed by the exerciser to emulate the behavior of a specific device. Simple export, edit and replay tools make the process easy. This allows the test engineer to build a library of test cases simply by capturing behavior from actual PCIe devices and play those back against the device under test to get a clear picture of the interoperability potential of a new design. By editing the replay file, specific error conditions can be created while also emulating a specific PCIe environment.

#### **Equalization and Transceiver Configuration**

The P5551A PCIe 5.0 Exerciser provides several options for controlling Link Equalization parameters which enable the user to create specific scenarios for testing link bring up. For 8 GT/s, 16GT/s and 32 GT/s the user can both specify parameters for the Exerciser to use and configure the Exerciser to make certain Equalization requests to the DUT such as:

- Adjustment to TX Pre/Post Cursor Coefficients for 8/16/32 GT/s

- Start Preset value

- · Specify a number of rejections of Presets to mimic difficulties in negotiation

- Apply specific presets to individual lanes at certain speeds.

- Programmable transceiver settings covering different amplitude and emphasis levels.

#### **Skip OS Configuration**

The P5551A PCIe 5.0 Exerciser supports Common Clock architecture. The user can configure Skip interval.

#### **Customized PCIe Traffic Generation**

With PCIe Exerciser mode, users can create customized Configuration Reads and Writes, I/O Reads and Writes, Memory Reads and Writes, Messages, and specific Completion types. Templates for each command type are provided to enable the user to create test cases quickly. The Traffic Setup interface in the P5551A allows I/O workloads and payloads to be created to simulate different conditions for the DUT and perform Performance Characterization.

#### **Power Management Features**

PCIe end users are paying more attention to power management at the device level. Ensuring proper entry and reliable exit of low power PCIe states is becoming ever more important. The P5551A provides superb capability for testing Power Management by providing precise and reliable stimulus for putting end devices in to L0, L0s, and L1 substates.

#### **Automation API**

Building customized test cases enables test engineers to fully vet the unique functionality of their products. Automating those test cases allows test engineers to accomplish more testing in less time, building confidence in the reliability of their designs. To enable this, the P5551A supports several scripting and automation capabilities that test engineers have asked for. The P5551A supports C# and Python APIs for scripting and automation.

#### **Product Specifications**

| <b>General Characteristics</b> |                                                                                                                                                                                                                                                                                                                                                                |  |  |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Link Widths                    | x1, x2, x4, x8, x16                                                                                                                                                                                                                                                                                                                                            |  |  |

| Data Rates                     | 2.5 GT/s (Gen1), 5.0 GT/s (Gen2), 8.0 GT/s (Gen3), 16.0 GT/s, (Gen4), and 32 GT/s(Gen5)                                                                                                                                                                                                                                                                        |  |  |

| Speed                          | 32 GBaud NRZ per lane                                                                                                                                                                                                                                                                                                                                          |  |  |

| Clocking Architecture          | Common Clock architecture                                                                                                                                                                                                                                                                                                                                      |  |  |

| Physical Characteristics       |                                                                                                                                                                                                                                                                                                                                                                |  |  |

| Size                           | (Standard height) half-length PCIe module 106.7 mm (4.2 inches) high and 167.65 mm (6.6 inches) long                                                                                                                                                                                                                                                           |  |  |

| Weight                         | 408 gr (0.9 lb)<br>Shipping weight: 2.36 Kg (5.2 lb)                                                                                                                                                                                                                                                                                                           |  |  |

| Connectors                     | Power input, USB 3.0, and two SMA(f) connectors for trigger in and out.  Edge connector width is determined by the Link Width configuration purchased.  Note: The edge connector is not upgradable after purchase and Keysight does not recommend or support the use of lane adaptors as they have a negative impact on the unit's performance at high speeds. |  |  |

| Cover                          | The hardware board has a cover to provide rigidness to the board.                                                                                                                                                                                                                                                                                              |  |  |

| Power requirements             |                                                                                                                                                                                                                                                                                                                                                                |  |  |

| Input                          | 12 Vdc, 14 A maximum                                                                                                                                                                                                                                                                                                                                           |  |  |

| Maximum power requirement      | 180 W                                                                                                                                                                                                                                                                                                                                                          |  |  |

| Power dissipation              | 150 W maximum                                                                                                                                                                                                                                                                                                                                                  |  |  |

| Keysight part number 0950      | 0-6474 external power supply supplied with the Exerciser                                                                                                                                                                                                                                                                                                       |  |  |

| Input                          | 100 to 240 V at 4.0 A maximum, 50 to 60 Hz                                                                                                                                                                                                                                                                                                                     |  |  |

| LTSSM uncurported states       |                                                                                                                                                                                                                                                                                                                                                                |  |  |

#### LTSSM unsupported states

The Keysight P5551A supports all of the LTSSM states except the following unsupported states:

- 12

- Loopback

| P5551A trigger specifications |                                     |  |  |

|-------------------------------|-------------------------------------|--|--|

| Trigger Output                |                                     |  |  |

| Output impedance              | 50 ohms                             |  |  |

| Threshold voltage             | VOH - 2.4V<br>VOL – 0.55V           |  |  |

| Amplitude                     | 2.4 V into open, 1.2 V into 50 ohms |  |  |

| Pulse width                   | 120 nS                              |  |  |

| Trigger input                 |                                     |  |  |

| Maximum input                 | 3.0 V                               |  |  |

| Threshold voltage (VIH)       | 2.0 V                               |  |  |

#### **Environmental specifications**

| This instrument is intended for indoor use in an installation category II, pollution degree 2 environment. |                                                                                             |  |  |  |

|------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--|--|--|

| Temperature                                                                                                | Operating: +5 °C to +35 °C<br>Storage: -40 °C to +70 °C                                     |  |  |  |

| Humidity                                                                                                   | Operating: 15 to 85% (Relative humidity) Storage: 15 to 95% (Relative humidity)             |  |  |  |

| Altitude                                                                                                   | 2000 m (6,500 feet) maximum                                                                 |  |  |  |

| EMC and Safety                                                                                             | IEC 61326-1<br>IEC 61010-1 / EN 61010-1<br>Canada: CSA C22.2 No. 61010-1<br>USA: UL 61010-1 |  |  |  |

#### **Additional Recommended Hardware**

While the Keysight P5551A PCIe 5.0 Protocol Exerciser is quite versatile as a stand alone test tool, more complicated test configurations can be supported when the P5551A is paired with additional Keysight hardware to improve analysis capability, robustness, and mechanical stability. Additional Keysight products that support the P5551A are shown below.

| Description                      | Keysight model number(s) | Comments |

|----------------------------------|--------------------------|----------|

| PCIe 5.0 Protocol Analyzer       | P5552A                   |          |

| PCle 5.0 Test System (Backplane) | P5563A                   |          |

| PCIe Card Holder                 | P5500A                   |          |

### **Ordering Information**

| Model       | Description                              | Comments                      |

|-------------|------------------------------------------|-------------------------------|

| P5551A-E04  | PCle 5.0 Exerciser Linkwidth x4          |                               |

| P5551A-E08  | PCIe 5.0 Exerciser Linkwidth x8          |                               |

| P5551A-E16  | PCIe 5.0 Exerciser Linkwidth x16         |                               |

| P5551PSWA   | PCIe 5.0 Exerciser Software              | Required for use of Exerciser |

| P5552A-A04  | PCIe 5.0 Analyzer Linkwidth x4           |                               |

| P5552A-A08  | PCIe 5.0 Analyzer Linkwidth x8           |                               |

| P5552A-A16  | PCIe 5.0 Analyzer Linkwidth x16          |                               |

| P5552PSWA   | PCIe 5.0 Analyzer Software               | Required for use of Analyzer  |

| R-55A-001-3 | KeysightCare Assured - Extend to 3 years |                               |

| P5563A      | PCIe 5.0 Test System (Backplane)         |                               |

| P5500A      | PCIe Card Holder                         |                               |

## Software Licensing and KeysightCare Software Support Subscriptions

Keysight offers a variety of licensing options to fit your needs and budget. Choose your license term, license type, and KeysightCare software support subscription.

#### **KeysightCare Software Support Subscriptions**

Perpetual licenses are sold with a 12 (default), 24, 36, or 60-month software support subscription. Support subscriptions can be renewed for a fee after that.

Contact your Keysight representative or authorized partner for more information or to place an order:

www.keysight.com/find/contactus

### **KeysightCare Software Support Subscription provides** peace of mind amid evolving technologies.

- Ensure your software is always current with the latest enhancements and measurement standards.

- Gain additional insight into your problems with live access to our team of technical experts.

- Stay on schedule with fast turnaround times and priority escalations when you need support.