产品手册

仪器型号: P5552A

西安安泰测试科技有限公司 仪器维修|租赁|销售|测试

地址:西安市高新区纬二十六路 369 号电话: 400-876-5512网址: www.agitekservice.com座机: 029-88827159

## P5552A

## **PCI Express Protocol Analyzer**

For PCIe 5.0

#### Introduction

The P5552A PCIe Protocol Analyzer enables deep protocol analysis of PCIe systems in a form factor that is easy to deploy on the lab bench and offers unparalleled signal integrity. The analyzer supports capture and decode for PCIe 1.0 through PCIe 5.0. When paired with the P5551A Protocol Exerciser, incredibly powerful PCIe validation solutions can be built.

## **Table of Contents**

| Introduction                                                       | 1  |

|--------------------------------------------------------------------|----|

| Table of Contents                                                  | 2  |

| Product Overview                                                   | 3  |

| Trusted Signal Integrity                                           | 4  |

| Convenient and Stable Form Factor                                  | 5  |

| Combined Exerciser and Analyzer Software                           | 6  |

| Use Case: Analyze Traffic between Root Complex and Endpoint        | 7  |

| Backplane Test Platform                                            | 7  |

| Powerful Triggering and Filtering                                  | 8  |

| Traffic Decode and Analysis Capability                             | 9  |

| Lane View                                                          | 9  |

| Performance Overview                                               | 10 |

| Transaction Decode                                                 | 10 |

| LTSSM Overview                                                     | 11 |

| Product Specifications                                             | 11 |

| Additional Recommended Hardware                                    | 12 |

| Ordering Information                                               | 13 |

| Software licensing and KeysightCare software support subscriptions | 14 |

#### **Product Overview**

The Keysight P5552A PCIe 5.0 Protocol Analyzer features an integrated interposer design which simplifies connection and offers improved signal integrity. By removing the need for a cumbersome external analyzer chassis, setup and versatility on the lab bench are greatly improved. Additionally, this simplified design yields superior signal integrity, ensuring that the analyzer has minimal impact on the channel between the products under test.

The P5552A supports decode of up to 32 GT/s signaling and lane widths of x4, x8 and x16. Users can utilize up to 16 GB trace depth memory aided by on-board compression which greatly expands the available capture time. The analyzer supports decode of the PHY Layer (TS1/TS2/Ordered sets, Link Layer (ACK,/NAK, sequencing numbers, replay, etc), and Transaction Layer (Memory, Config, and I/O Read and Writes operations, etc)

Figure 1. P5552A PCIe 5.0 Protocol Analyzer

### **Trusted Signal Integrity**

Debugging complicated interoperability issues between a PCIe Host and Device requires that any protocol analyzer interposer not disrupt the interactions between a Host and Device. The foundation of this in the P5552A is superb control of signal integrity with built in equalization and amplification that effectively removes the effects of the analyzer from the link. This provides the user with confidence that the traffic observed between the Host System and Endpoint are exactly as if the analyzer were not present.

Other analyzer designs that rely on a separate analyzer chassis often introduce physical and electrical complexities that can impact the channel. In some cases, these interposers inadvertently add channel impairments which can affect the system under test such that it cannot reliably negotiate to the highest mutually supported speeds and lane width. In other cases, an interposer may introduce retiming or redriving capability that can mask issues in the system under test by effectively improving the channel quality and enabling devices to successfully link up in configurations that could not be attainable without the analyzer present. Neither of these conditions is acceptable as they impede the ability of the test and validation engineer to gain a clear and accurate view of what is happening on the link.

The Keysight P5552A was designed deliberately to avoid these issues, to minimize channel impact and to provide the clearest and most accurate view of the traffic on the PCIe link. Thus, test and validation engineers can focus time and energy on solving protocol issues between the products under test, rather than questioning whether issues have been introduced or masked by their test equipment.

#### Convenient and Stable Form Factor

The single card design of the Keysight P5552A PCIe 5.0 Protocol Analyzer enables a convenient and fast setup on the lab bench. Often test configurations on the lab bench quickly become complicated, and mechanical stability of prototype devices is critical to ensure that early product samples are physically protected and that the mechanical connection between the analyzer and the products under test is solid and robust and not introducing any signal impairments due to lack of mechanical stability. The P5552A is provided with a bracket mount that enables secure attachment a server chassis. Additionally, attention has been given to providing mechanical security to add-in-card endpoints that are included in the test setup via an additional stability bracket.

Figure 2. P5552A PCle 5.0 Protocol Analyzer

Above the standard PCIe server mounting bracket, an additional mount point is provided to attach the Keysight P5500A Card Holder. This card holder ensures a secure mechanical connection between an add-in-card and the P5552A Analyzer. Further, it provides physical protection to the add-in-card. Often, products under test on the lab bench are part of limited prototype runs, and the loss of a single unit to poor mechanical stability is a real risk to product validation timelines. The Keysight P5552A PCIe 5.0 Protocol Analyzer enables test and validation engineers to mitigate those risks while ensuring a solid mechanical connection. This eliminates doubts from the validation process and ensures that engineers are not chasing problems introduced by a poorly designed mechanical setup that introduces electrical and protocol errors due to instability.

Figure 3. PCle Card Holder provides mechanical stability.

## **Combined Exerciser and Analyzer Software**

Both the Keysight PCIe 5.0 P5551A Protocol Exerciser and P5552A Analyzer can be driven by a single combined software interface which with provides enhanced Exerciser Functionality for configuring Traffic Setup and improved data exchange with the analyzer.

Via this thoughtfully designed interface, the user can configure all of the most important characteristics of the PCIe link such as lane width and link speed.

Figure 4. Combined software interface for Analyzer and Exerciser functions.

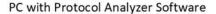

# Use Case: Analyze Traffic between Root Complex and Endpoint

A common use case for the Keysight P5552A PCle 5.0 Analyzer is to sit between a PCle 5.0 capable root complex and a PCle 5.0 endpoint. The analyzer will capture and decode PCle signals between the root complex and the endpoint while also passing the signals between the devices through without interference.

The Keysight P5552A Analyzer uses an independent power supply, and passes power suppled from the Host System on to the Endpoint without interference.

Figure 5. Use the P5552A to analyze PCIe traffic between a Root Complex and Endpoint.

#### **Backplane Test Platform**

The Keysight P5563A PCIe 5.0 Protocol Backplane Test Platform features SI enhancements to reduce crosstalk and improve signal integrity, where low-loss material in utilized to support reliable connections at 32GT/s.

- CEM form factor for endpoint devices. Automated link training to 32GT/s

- Integrated low noise power supply with Auxiliary PCIe power available for high power endpoint devices

- Stable mechanical construction for reliable operation during bring-up

- One pair of CEM slots for connecting the Exerciser with a DUT.

Figure 6. P5563A Backplane Test Platform.

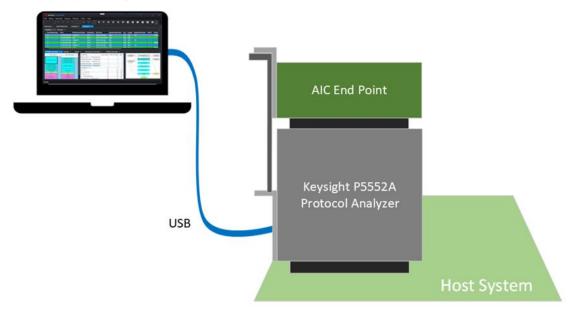

### **Powerful Triggering and Filtering**

The most difficult bugs to solve are intermittent with no obvious cause. Finding the root of these troublesome issues often involves setting up for long capture times. But capturing lots of data is not helpful if it cannot effectively be analyzed. Scrolling through trace captures looking for specific issues that are obscured by retraining events and other protocol 'storms' is an ineffective use of time.

Advanced users depend on finely tuned triggering and filtering settings to capture the traffic that they are most interested in. They avoid massive capture windows that scoop up unwanted data which slows down the analysis process both in porting the data to a PC for viewing as well as needlessly obscuring critical protocol events. The Keysight P5552A PCIe 5.0 Protocol Analyzer was designed with this use case in mind. As such, it provides both Simple and Advanced triggering modes. Simple triggers are provided that are quick for users to apply and customize. Advanced Triggers can be configured to apply a chain of If/Then logic steps to the trigger. In this way specific protocol events can be captured easily, even if they occur only after a complex series of previous events that may span a long time period.

To extend this capability even further filtering can be applied to ignore certain traffic events to extend the capture window without clogging up the capture log with unneeded data.

Figure 7. Analyzer Trigger configuration window.

### **Traffic Decode and Analysis Capability**

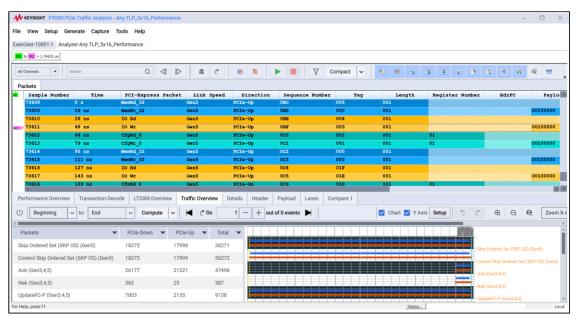

Solving protocol issues involves a variety of skill sets and debugging tools. Some issues require being able to see specific fields in a packet. Other problems require having an overall view of traffic patterns and errors in a given time frame. To support these needs the Keysight P5552A PCIe 5.0 Protocol Analyzer software provides several different protocol views to enable engineers to use the tool most suited to the problems they are working on.

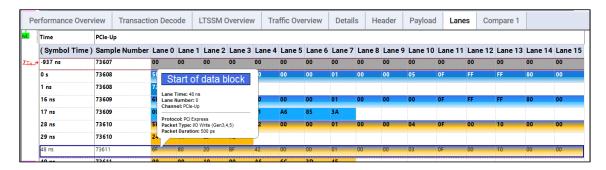

#### **Lane View**

Lane view provides the user with a view of exactly what data is appearing on which lane of the PCIe link. With a mouse over the user can see what packet types individual bytes are associated with. Thus, in a single simple view, the user is given a comprehensive understanding of the protocol makeup.

Figure 8. PCIe Protocol Analyzer Lane View

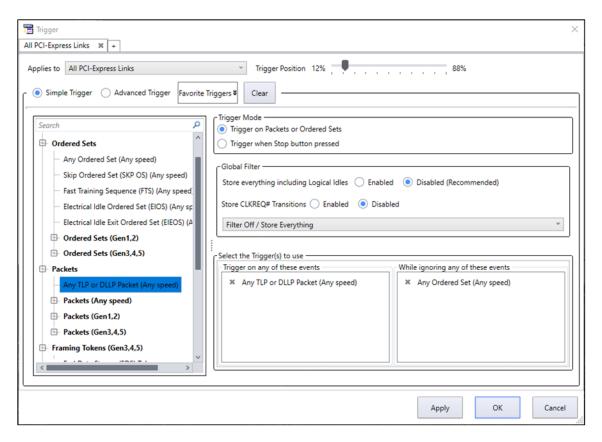

#### **Performance Overview**

The Performance Overview tab provides a visual depiction of different PCIe protocol events over time. The user is given a clear understanding of throughput performance, flow control and completed /transactions.

Figure 9. PCIe Protocol Analyzer Performance View

#### **Transaction Decode**

The Transaction Decode tab provides a detailed view of how individual packets are organized into a transaction. The initial packet operation, acknowledgement, and completion are condensed into a single line in the Transaction Decode view, which can easily be expanded to see each packet atomically. The transaction based view can be much more intuitive to look at than the chronological order of packets provided in the Packet view, and gives the user a deeper understanding of the protocol.

Figure 10. PCIe Protocol Analyzer Transaction Decode View

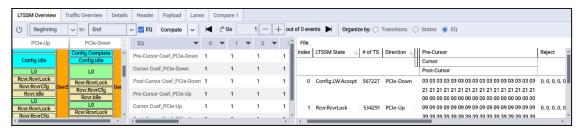

#### LTSSM Overview

Proper Link Training is critical to solid PCIe performance, and it is often the source of many issues. Physical differences in channels and products are manifested at the protocol layer via the LTSSM. The LTSSM Overview allows validation engineers to see progression through the LTSSM and a decode of which state both the Upstream and Downstream ports are in at a given moment. The LTSSM Overview is a powerful tool for debugging one of the most difficult and complex aspects of PCIe protocol.

Figure 11. PCIe Protocol Analyzer LTSSM Overview

### **Product Specifications**

| General characteristics                   |                                                                                                                                                                                                                 |  |  |

|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Link widths                               | x1, x2, x4, x8, x16 with x16 PCle Edge connector                                                                                                                                                                |  |  |

| Data rates                                | 2.5 GT/s (Gen1), 5.0 GT/s (Gen2), 8.0 GT/s (Gen3), 16.0 GT/s, (Gen4), and 32 GT/s(Gen5)                                                                                                                         |  |  |

| Speed                                     | 32 GBaud NRZ per lane                                                                                                                                                                                           |  |  |

| Clocking architecture                     | Common Clock architecture                                                                                                                                                                                       |  |  |

| Physical characteristics                  |                                                                                                                                                                                                                 |  |  |

| Size                                      | (Standard height) half-length PCIe module 235 mm high and 167 mm long                                                                                                                                           |  |  |

| Weight                                    | < 1.5 Kg                                                                                                                                                                                                        |  |  |

| Connectors                                | Power input, USB 3.0, and two SMA(f) connectors for trigger in and out.                                                                                                                                         |  |  |

| Cover                                     | The hardware board has a cover to provide rigidness to the board.                                                                                                                                               |  |  |

| Power requirements                        |                                                                                                                                                                                                                 |  |  |

| Input                                     | 12 Vdc, 18 A maximum                                                                                                                                                                                            |  |  |

| Maximum power requirement                 | 230 W                                                                                                                                                                                                           |  |  |

| P5552A specifications and characteristics |                                                                                                                                                                                                                 |  |  |

| PCIe Edge Finger for system DUT           | Consists of PCIe Gen6 x 16 PCB edge finger to support single slot PCIE card. The PCB has 82 gold-plated pins on top and 82 gold-plated pins on the bottom to support 164 pins, a requirement for PCIe x16 slot. |  |  |

| Trigger output                            |                                                                                                                                                                                                                 |  |  |

| Output impedance                     | 50 ohms                                                                                                                                 |  |  |  |

|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Threshold voltage                    | VOH - 2.4 V; VOL – 0.55 V                                                                                                               |  |  |  |

| Trigger input                        |                                                                                                                                         |  |  |  |

| Maximum input                        | 3.0 V                                                                                                                                   |  |  |  |

| Threshold voltage (VIH)              | 2.0 V                                                                                                                                   |  |  |  |

| Environmental specifications         |                                                                                                                                         |  |  |  |

| This instrument is intended for indo | or use in an installation category II, pollution degree 2 environment.                                                                  |  |  |  |

|                                      |                                                                                                                                         |  |  |  |

| Temperature                          | Operating: +5 °C to +35 °C; Storage: -40 °C to +70 °C                                                                                   |  |  |  |

| Temperature Humidity                 | Operating: +5 °C to +35 °C; Storage: -40 °C to +70 °C  Operating: 15 to 85% (Relative humidity)  Storage: 15 to 95% (Relative humidity) |  |  |  |

|                                      | Operating: 15 to 85% (Relative humidity)                                                                                                |  |  |  |

## **Additional Recommended Hardware**

While the Keysight P5552A PCIe 5.0 Protocol Analyzer offers deep insight into the interactions of PCIe Root Complex and Endpoint devices, even more powerful test configurations can be supported when the P5552A is paired with additional Keysight hardware to improve test case customization, robustness, and mechanical stability. Additional Keysight products that can accompany the P5552A are shown below.

| Description                      | Keysight model number(s) | Comments |

|----------------------------------|--------------------------|----------|

| PCIe 5.0 protocol exerciser      | P5551A                   |          |

| PCIe 5.0 test system (backplane) | P5563A                   |          |

| PCIe card holder                 | P5500A                   |          |

## **Ordering Information**

| Model       | Description                              | Comments                         |

|-------------|------------------------------------------|----------------------------------|

| P5551A-E04  | PCIe 5.0 Exerciser Linkwidth x4          |                                  |

| P5551A-E08  | PCIe 5.0 Exerciser Linkwidth x8          |                                  |

| P5551A-E16  | PCIe 5.0 Exerciser Linkwidth x16         |                                  |

| P5551PSWA   | PCIe 5.0 Exerciser Software              | Required for use of<br>Exerciser |

| P5552A-A04  | PCIe 5.0 Analyzer Linkwidth x4           |                                  |

| P5552A-A08  | PCIe 5.0 Analyzer Linkwidth x8           |                                  |

| P5552A-A16  | PCIe 5.0 Analyzer Linkwidth x16          |                                  |

| P5552PSWA   | PCIe 5.0 Analyzer Software               | Required for use of<br>Analyzer  |

| R-55A-001-3 | KeysightCare Assured - Extend to 3 years |                                  |

| P5563A      | PCIe 5.0 Test System (Backplane)         |                                  |

| P5500A      | PCIe Card Holder                         | _                                |

# Software licensing and KeysightCare software support subscriptions

Keysight offers a variety of licensing options to flit your needs and budget. Choose your license term, license type, and KeysightCare software support subscription.

KeysightCare software support subscriptions

Perpetual licenses are sold with a 12 (default), 24, 36, or 60-month software support subscription. Support subscriptions can be renewed for a fee after that.

Contact your Keysight representative or authorized partner for more information or to place an order:

www.keysight.com/find/contactus

For more information about Keysight's PCIe solutions, go to:

www.keysight.com/find/pcie

## KeysightCare Software Support Subscription provides peace of mind amid evolving technologies.

- Ensure your software is always current with the latest enhancements and measurement standards.

- Gain additional insight into your problems with live access to our team of technical experts.

- Stay on schedule with fast turnaround times and priority escalations when you need support.

Keysight enables innovators to push the boundaries of engineering by quickly solving design, emulation, and test challenges to create the best product experiences. Start your innovation journey at <a href="https://www.keysight.com">www.keysight.com</a>.