# NI sbRIO-9651

System on Module Carrier Board Design Guide

March 2017 376960C-01

#### Worldwide Technical Support and Product Information

ni.com

#### Worldwide Offices

Visit ni.com/niglobal to access the branch office websites, which provide up-to-date contact information, support phone numbers, email addresses, and current events.

#### National Instruments Corporate Headquarters

11500 North Mopac Expressway Austin, Texas 78759-3504 USA Tel: 512 683 0100

For further support information, refer to the *NI Services* appendix. To comment on National Instruments documentation, refer to the National Instruments website at ni.com/info and enter the Info Code feedback.

© 2014–2017 National Instruments. All rights reserved.

#### Limited Warranty

This document is provided 'as is' and is subject to being changed, without notice, in future editions. For the latest version, refer to ni.com/manuals. NI reviews this document carefully for technical accuracy; however, NI MAKES NO EXPRESS OR IMPLIED WARRANTIES AS TO THE ACCURACY OF THE INFORMATION CONTAINED HEREIN AND SHALL NOT BE LIABLE FOR ANY ERRORS.

NI warrants that its hardware products will be free of defects in materials and workmanship that cause the product to fail to substantially conform to the applicable NI published specifications for one (1) year from the date of invoice.

For a period of ninety (90) days from the date of invoice, NI warrants that (i) its software products will perform substantially in accordance with the applicable documentation provided with the software and (ii) the software media will be free from defects in materials and workmanship.

If NI receives notice of a defect or non-conformance during the applicable warranty period, NI will, in its discretion: (i) repair or replace the affected product, or (ii) refund the fees paid for the affected product. Repaired or replaced Hardware will be warranted for the remainder of the original warranty period or ninety (90) days, whichever is longer. If NI elects to repair or replace the product, NI may use new or refurbished parts or products that are equivalent to new in performance and reliability and are at least functionally equivalent to the original part or product.

You must obtain an RMA number from NI before returning any product to NI. NI reserves the right to charge a fee for examining and testing Hardware not covered by the Limited Warranty.

This Limited Warranty does not apply if the defect of the product resulted from improper or inadequate maintenance, installation, repair, or calibration (performed by a party other than NI); unauthorized modification; improper environment; use of an improper hardware or software key; improper use or operation outside of the specification for the product; improper voltages; accident, abuse, or neglect; or a hazard such as lightning, flood, or other act of nature.

THE REMEDIES SET FORTH ABOVE ARE EXCLUSIVE AND THE CUSTOMER'S SOLE REMEDIES, AND SHALL APPLY EVEN IF SUCH REMEDIES FAIL OF THEIR ESSENTIAL PURPOSE.

EXCEPT AS EXPRESSLY SET FORTH HEREIN, PRODUCTS ARE PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND AND NI DISCLAIMS ALL WARRANTIES, EXPRESSED OR IMPLIED, WITH RESPECT TO THE PRODUCTS, INCLUDING ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE OR NON-INFRINGEMENT, AND ANY WARRANTIES THAT MAY ARISE FROM USAGE OF TRADE OR COURSE OF DEALING. NI DOES NOT WARRANT, GUARANTEE, OR MAKE ANY REPRESENTATIONS REGARDING THE USE OF OR THE RESULTS OF THE USE OF THE PRODUCTS IN TERMS OF CORRECTNESS, ACCURACY, RELIABILITY, OR OTHERWISE. NI DOES NOT WARRANT THAT THE OPERATION OF THE PRODUCTS WILL BE UNINTERRUPTED OR ERROR FREE.

In the event that you and NI have a separate signed written agreement with warranty terms covering the products, then the warranty terms in the separate agreement shall control.

#### Copyright

Under the copyright laws, this publication may not be reproduced or transmitted in any form, electronic or mechanical, including photocopying, recording, storing in an information retrieval system, or translating, in whole or in part, without the prior written consent of National Instruments Corporation.

National Instruments respects the intellectual property of others, and we ask our users to do the same. NI software is protected by copyright and other intellectual property laws. Where NI software may be used to reproduce software or other materials belonging to others, you may use NI software only to reproduce materials that you may reproduce in accordance with the terms of any applicable license or other legal restriction.

#### End-User License Agreements and Third-Party Legal Notices

You can find end-user license agreements (EULAs) and third-party legal notices in the following locations:

- Notices are located in the <National Instruments>\\_Legal Information and <National Instruments> directories.

- EULAs are located in the <National Instruments>\Shared\MDF\Legal\license directory.

- Review <National Instruments>\\_Legal Information.txt for information on including legal information in

installers built with NI products.

#### U.S. Government Restricted Rights

If you are an agency, department, or other entity of the United States Government ("Government"), the use, duplication, reproduction, release, modification, disclosure or transfer of the technical data included in this manual is governed by the Restricted Rights provisions under Federal Acquisition Regulation 52.227-14 for civilian agencies and Defense Federal Acquisition Regulation S2.227-7015 for military agencies.

#### Trademarks

Refer to the *NI Trademarks and Logo Guidelines* at ni.com/trademarks for more information on National Instruments trademarks.

ARM, Keil, and µVision are trademarks or registered trademarks of ARM Ltd or its subsidiaries.

LEGO, the LEGO logo, WEDO, and MINDSTORMS are trademarks of the LEGO Group.

TETRIX by Pitsco is a trademark of Pitsco, Inc.

FIELDBUS FOUNDATION<sup>™</sup> and FOUNDATION<sup>™</sup> are trademarks of the Fieldbus Foundation.

EtherCAT® is a registered trademark of and licensed by Beckhoff Automation GmbH.

CANopen® is a registered Community Trademark of CAN in Automation e.V.

DeviceNet<sup>™</sup> and EtherNet/IP<sup>™</sup> are trademarks of ODVA.

Go!, SensorDAQ, and Vernier are registered trademarks of Vernier Software & Technology. Vernier Software & Technology and vernier.com are trademarks or trade dress.

Xilinx is the registered trademark of Xilinx, Inc.

Taptite and Trilobular are registered trademarks of Research Engineering & Manufacturing Inc.

FireWire® is the registered trademark of Apple Inc.

Linux® is the registered trademark of Linus Torvalds in the U.S. and other countries.

Handle Graphics<sup>®</sup>, MATLAB<sup>®</sup>, Real-Time Workshop<sup>®</sup>, Simulink<sup>®</sup>, Stateflow<sup>®</sup>, and xPC TargetBox<sup>®</sup> are registered trademarks, and TargetBox<sup>™</sup> and Target Language Compiler<sup>™</sup> are trademarks of The MathWorks, Inc.

Tektronix®, Tek, and Tektronix, Enabling Technology are registered trademarks of Tektronix, Inc.

The Bluetooth® word mark is a registered trademark owned by the Bluetooth SIG, Inc.

The ExpressCard<sup>™</sup> word mark and logos are owned by PCMCIA and any use of such marks by National Instruments is under license.

The mark LabWindows is used under a license from Microsoft Corporation. Windows is a registered trademark of Microsoft Corporation in the United States and other countries.

Other product and company names mentioned herein are trademarks or trade names of their respective companies.

Members of the National Instruments Alliance Partner Program are business entities independent from National Instruments and have no agency, partnership, or joint-venture relationship with National Instruments.

#### Patents

For patents covering National Instruments products/technology, refer to the appropriate location: **Help»Patents** in your software, the patents.txt file on your media, or the *National Instruments Patent Notice* at ni.com/patents.

#### Export Compliance Information

Refer to the *Export Compliance Information* at ni.com/legal/export-compliance for the National Instruments global trade compliance policy and how to obtain relevant HTS codes, ECCNs, and other import/export data.

#### WARNING REGARDING USE OF NATIONAL INSTRUMENTS PRODUCTS

YOU ARE ULTIMATELY RESPONSIBLE FOR VERIFYING AND VALIDATING THE SUITABILITY AND RELIABILITY OF THE PRODUCTS WHENEVER THE PRODUCTS ARE INCORPORATED IN YOUR SYSTEM OR APPLICATION, INCLUDING THE APPROPRIATE DESIGN, PROCESS, AND SAFETY LEVEL OF SUCH SYSTEM OR APPLICATION.

PRODUCTS ARE NOT DESIGNED, MANUFACTURED, OR TESTED FOR USE IN LIFE OR SAFETY CRITICAL SYSTEMS, HAZARDOUS ENVIRONMENTS OR ANY OTHER ENVIRONMENTS REQUIRING FAIL-SAFE PERFORMANCE, INCLUDING IN THE OPERATION OF NUCLEAR FACILITIES; AIRCRAFT NAVIGATION; AIR TRAFFIC CONTROL SYSTEMS; LIFE SAVING OR LIFE SUSTAINING SYSTEMS OR SUCH OTHER MEDICAL DEVICES; OR ANY OTHER APPLICATION IN WHICH THE FAILURE OF THE PRODUCT OR SERVICE COULD LEAD TO DEATH, PERSONAL INJURY, SEVERE PROPERTY DAMAGE OR ENVIRONMENTAL HARM (COLLECTIVELY, "HIGH-RISK USES"). FURTHER, PRUDENT STEPS MUST BE TAKEN TO PROTECT AGAINST FAILURES, INCLUDING PROVIDING BACK-UP AND SHUT-DOWN MECHANISMS. NI EXPRESSLY DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY OF FITNESS OF THE PRODUCTS OR SERVICES FOR HIGH-RISK USES.

# Contents

### About This Document

| Terminology                        | . ix |

|------------------------------------|------|

| Schematic Conventions              |      |

| Additional Documentation Resources | . xi |

# Chapter 1 Fixed Behavior Signals

| Primary Ethernet (GBE0)                                   | . 1-1  |

|-----------------------------------------------------------|--------|

| GBE0 Signal Definitions                                   | . 1-2  |

| GBE0 Implementation on the Reference Carrier Board        | . 1-3  |

| Gigabit Ethernet Magnetic Requirements                    | . 1-4  |

| GBE0 Routing Considerations                               |        |

| USB (USB0, USB1)                                          | . 1-5  |

| USB0 Host/Device Signal Definitions                       | . 1-5  |

| USB0 Device Implementation on the Reference Carrier Board | . 1-6  |

| USB1 Host Signal Definitions                              |        |

| USB1 Host Implementation on the Reference Carrier Board   | . 1-8  |

| Supporting Onboard USB Devices                            |        |

| USB Routing Considerations                                | . 1-10 |

| UART/Console Out (Serial1)                                | . 1-10 |

| Serial1 Signal Definitions                                | . 1-10 |

| Serial1 Implementation on the Reference Carrier Board     | . 1-11 |

| Adding Flow Control and Modem Control Signals             | . 1-12 |

| SD Card                                                   | . 1-12 |

| SD Signal Definitions                                     | . 1-13 |

| SD Implementation on the Reference Carrier Board          | . 1-14 |

| SD Routing Considerations                                 | . 1-16 |

| RTC Battery (VBAT)                                        | . 1-16 |

| VBAT Signal Definitions                                   | . 1-17 |

| VBAT Implementation on the Reference Carrier Board        | . 1-17 |

| Eliminating the Effects of Contact Bounce                 | . 1-17 |

| Resets                                                    | . 1-18 |

| Reset Signal Definitions                                  | . 1-18 |

| Reset Implementation on the Reference Carrier Board       | . 1-19 |

| Status LED.                                               | . 1-20 |

| Status LED Signal Definitions                             | . 1-20 |

| Status LED Implementation on the Reference Carrier Board  | . 1-20 |

| FPGA Config                                               | . 1-21 |

| FPGA Config Signal Definitions                            | . 1-21 |

| FPGA Config Implementation on the Reference Carrier Board | . 1-21 |

| Temp Alert                                                | . 1-22 |

| Temp Alert Signal Definitions                             | . 1-22 |

| Temp Alert Implementation on the Reference Carrier Board  | . 1-22 |

# Chapter 2

### User-Defined FPGA Signals

| Secondary Ethernet (GBE1)                                 | 2-1  |

|-----------------------------------------------------------|------|

| GBE1 Signal Definitions on the Reference Carrier Board    |      |

| GBE1 Reference Schematic                                  | 2-4  |

| GBE1 Routing Considerations                               |      |

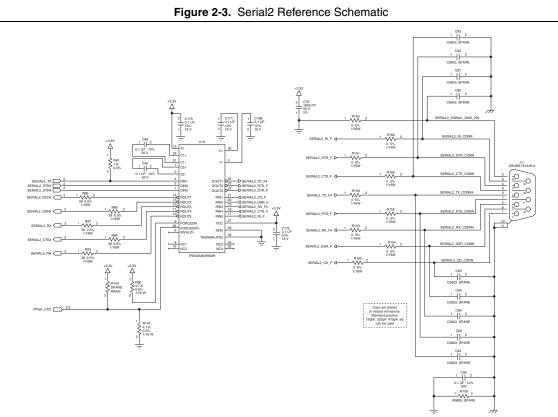

| Additional RS-232 (Serial2, Serial3, Serial4)             | 2-9  |

| Serial2 Signal Definitions on the Reference Carrier Board |      |

| Serial2 Reference Schematic                               |      |

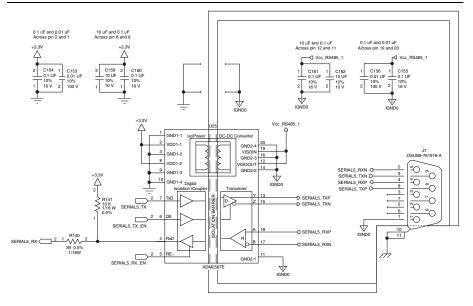

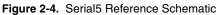

| RS-485 (Serial5, Serial6)                                 | 2-11 |

| Serial5 Definitions on the Reference Carrier Board        |      |

| Serial5 Reference Schematic                               |      |

| RS-485 Layout Considerations                              | 2-14 |

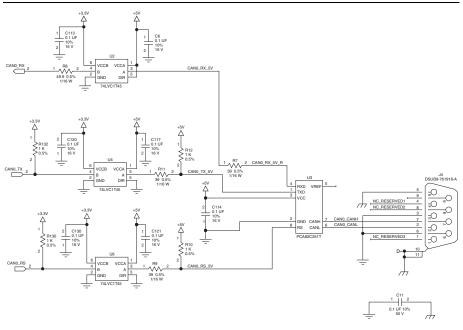

| CAN (CAN0, CAN1)                                          |      |

| CAN0 Signal Definitions on the Reference Carrier Board    |      |

| CAN0 Reference Schematic                                  |      |

| Termination Resistors for CAN Cables                      |      |

|                                                           |      |

#### Chapter 3 Carrier Board PCB Layout Guidelines

| Impedance-Controlled Signaling         | 3-1 |

|----------------------------------------|-----|

| Single-Ended Signal Best Practices     | 3-2 |

| Differential Signal Best Practices     | 3-2 |

| Ground and Power Plane Recommendations | 3-3 |

| Fanout and Layout Options              | 3-3 |

|                                        |     |

# Chapter 4

### Mechanical Considerations

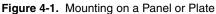

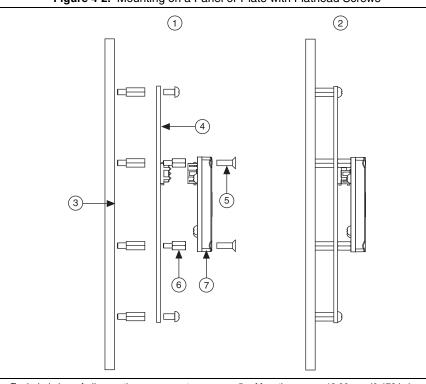

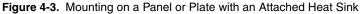

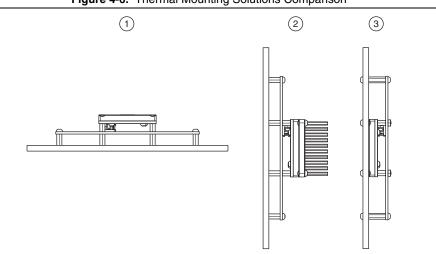

| Mounting                                                    | 4-1  |

|-------------------------------------------------------------|------|

| Selecting an Appropriate Mating Connector                   | 4-1  |

| Selecting Appropriate Standoffs                             | 4-2  |

| Mounting Direction Options                                  | 4-4  |

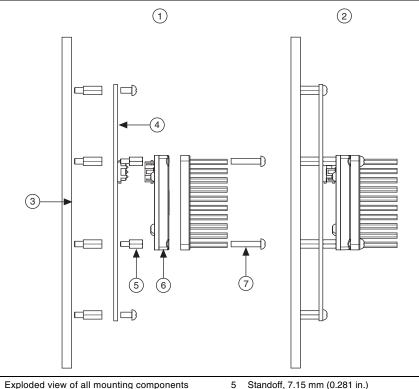

| Managing Thermal Conditions                                 | 4-6  |

| Designing a Suitable Enclosure                              | 4-6  |

| Understanding Thermal Specifications                        | 4-7  |

| Validating the System                                       | 4-8  |

| Validating Temperature Measurements                         | 4-8  |

| Managing Power and Feature Utilization                      | 4-10 |

| Mounting Recommendations for Maximizing Thermal Performance | 4-11 |

| Additional Resources for Managing Thermal Conditions        | 4-12 |

| Shock and Vibration                                         |      |

|                                                             |      |

| Appendix A                                            |     |

|-------------------------------------------------------|-----|

| Reference Carrier Board Specifications and User Guide |     |

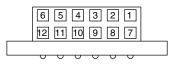

| Parts Locator Diagram and Block Diagram               |     |

| Specifications                                        | A-1 |

| Ethernet                                              | A-2 |

| Serial                                                | A-2 |

| CAN                                                   | A-2 |

| SD Card                                               | A-2 |

| USB                                                   | A-2 |

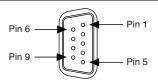

| Pmod                                                  | A-2 |

| RTC Battery                                           | A-4 |

| Support Signals                                       | A-4 |

| Connector Pinouts                                     | A-4 |

| RS-232, RS-485, and CAN Connector Pinouts             | A-4 |

| Pmod 12-Pin Connector Pinout                          | A-5 |

| Pmod I <sup>2</sup> C Connector Pinout                | A-6 |

| Environmental Management                              | A-6 |

### Appendix B **Revision History**

Appendix C NI Services

# About This Document

The NI sbRIO-9651 System on Module (SOM) provides an embedded real-time processor and reconfigurable FPGA. The sbRIO-9651 SOM requires a user-designed carrier board to provide power and I/O interfaces. You can optimize the carrier board to implement the exact functions your application requires. You can design the carrier board size and connector locations to fit the packaging or enclosure of your specific system.

This document provides detailed information about carrier board design techniques, guidelines, and requirements.

**Note** Refer to the documents listed in the *Additional Documentation Resources* section of this chapter for more information as you design, prototype, and implement your sbRIO-9651 SOM application. In particular, refer to the *NI sbRIO-9651 System* on *Module OEM Device Specifications* for dimensions, pinout information, functional specifications, and electrical specifications for the sbRIO-9651 SOM.

# Terminology

Table 1 defines terms used in this document to describe sbRIO-9651 SOM concepts and technology.

| Term              | Definition                                                                                              |  |  |  |

|-------------------|---------------------------------------------------------------------------------------------------------|--|--|--|

| System Components |                                                                                                         |  |  |  |

| J1                | Molex 45971-4185 320-pin, 8 × 40 position, SEARAY open-pin-field-array connector on the sbRIO-9651 SOM. |  |  |  |

| SEARAY            | Connector family used for the J1 connector on the sbRIO-9651 SOM.<br>Manufactured by Samtec and Molex.  |  |  |  |

| SOM               | System on Module.                                                                                       |  |  |  |

| SoC               | System on Chip.                                                                                         |  |  |  |

| USB Device        | Physical, electrical, addressable, and logical entity that is attached to USB and performs a function.  |  |  |  |

| USB Device port   | Port on a carrier board that provides a USB Device interface to the SOM.                                |  |  |  |

| USB Host          | USB interface that controls the bus and communicates with connected USB devices.                        |  |  |  |

| USB Host port     | Port on a carrier board that provides a USB Host interface from the SOM.                                |  |  |  |

#### Table 1. sbRIO-9651 SOM Terminology in This Document

| Term Definition                                                                                                            |                                                                                                                                                                                                                                            |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Reference Schematic and Signal Naming                                                                                      |                                                                                                                                                                                                                                            |  |  |  |

| LVTTL                                                                                                                      | In compliance with the Low-Voltage Transistor-Transistor Logic (LVTTL) specification.                                                                                                                                                      |  |  |  |

| LVCMOS                                                                                                                     | In compliance with the Low-Voltage Complementary Metal Oxide Semiconductor (LVCMOS) specification.                                                                                                                                         |  |  |  |

| PUDC                                                                                                                       | PUDC Pull-up During Configuration                                                                                                                                                                                                          |  |  |  |

|                                                                                                                            | Mechanical                                                                                                                                                                                                                                 |  |  |  |

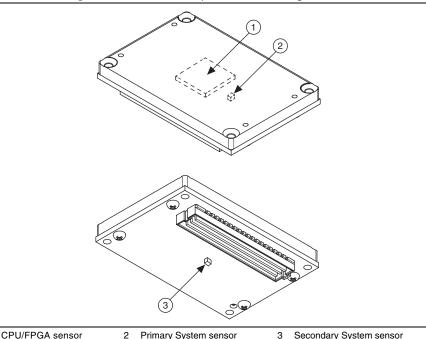

| CPU/FPGA The temperature reported digitally by a sensor that measures the die junction temperature of the Xilinx Zynq SoC. |                                                                                                                                                                                                                                            |  |  |  |

| Primary System<br>temperature                                                                                              | The temperature reported digitally by a sensor on the Xilinx Zynq SoC side of the circuit card assembly underneath the integrated heat spreader. This value is an approximation of the local ambient temperature inside the heat spreader. |  |  |  |

| Secondary System<br>temperature                                                                                            | The temperature reported digitally by a sensor on the SEARAY side<br>of the circuit card assembly. This value is a conservative<br>approximation of the local ambient temperature on that side of the<br>circuit card assembly.            |  |  |  |

#### Table 1. sbRIO-9651 SOM Terminology in This Document (Continued)

# Schematic Conventions

Table 2 describes symbol conventions used in the I/O interface schematic diagrams in this document.

| Symbol    | Description                                                                     |  |  |  |  |

|-----------|---------------------------------------------------------------------------------|--|--|--|--|

| $\sim$    | Off-page symbol that represents communication to and from the mating connector. |  |  |  |  |

| $\square$ | Off-page symbol that represents communication from the mating connector.        |  |  |  |  |

| Ċ-        | Off-page symbol that represents communication to the mating connector.          |  |  |  |  |

| D         | On-page symbol that represents the signal being driven.                         |  |  |  |  |

Table 2.

Schematic Conventions in This Document

| Symbol       | Description                                               |  |  |  |

|--------------|-----------------------------------------------------------|--|--|--|

|              | On-page symbol that represents the signal being received. |  |  |  |

| Ŷ            | Power supply rail.                                        |  |  |  |

| $\downarrow$ | Analog ground.                                            |  |  |  |

| Ļ            | Digital ground.                                           |  |  |  |

| /11          | Chassis ground.                                           |  |  |  |

| SPARE        | Refers to an unpopulated reference designator.            |  |  |  |

Table 2. Schematic Conventions in This Document (Continued)

# Additional Documentation Resources

Refer to the following additional resources as you design, prototype, and implement your sbRIO-9651 SOM application.

| What Would You Like to<br>Learn More About?                                                                                      | Resources                                                           | Availability |  |

|----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|--------------|--|

| NI sbRIO-9651<br>System on Module OEM Device                                                                                     | NI sbRIO-9651 System on Module<br>OEM Device Specifications         | POF          |  |

| NI sbRIO-9651<br>System on Module Development Kit                                                                                | NI sbRIO-9651 System on Module<br>Development Kit Quick Start Guide |              |  |

| Designing a carrier board for your application                                                                                   | NI sbRIO-9651 System on Module<br>Carrier Board Design Guide        | POF          |  |

| Adding an sbRIO-9651<br>System on Module target in LabVIEW                                                                       | LabVIEW Help (NI-RIO)                                               |              |  |

| Creating a socketed CLIP that defines the I/O configuration to use in your application                                           | NI Single-Board RIO CLIP<br>Generator Help                          |              |  |

| NI Training and Support                                                                                                          | ni.com/singleboard/setup<br>ni.com/training<br>ni.com/support       |              |  |

| PDF available online at ni.com/manuals 👔 Help file available locally 💱 Included in the shipping kit 🔇 Available online at ni.com |                                                                     |              |  |

# 1

# **Fixed Behavior Signals**

A subset of pins on the J1 connector on the sbRIO-9651 SOM are dedicated to implementing the following specific I/O functionality:

- Primary Ethernet (GBE0)

- USB Host/Device (USB0)

- USB Host (USB1)

- UART/Console Out (Serial1)

- SD Card

Other pins on the J1 connector are dedicated to implementing the following support signals:

- RTC Battery (VBAT)

- Resets

- Status LED

- FPGA Config

- Temp Alert

**Note** Refer to the *NI sbRIO-9651 System on Module OEM Device Specifications* for a complete list of all pins and signals on the J1 connector.

The reference carrier board included with the sbRIO-9651 SOM development kit demonstrates how to implement each of these signals. Refer to the specific sections in this chapter for more information about how the reference carrier board implements each signal.

# Primary Ethernet (GBE0)

The sbRIO-9651 SOM provides a primary Gigabit Ethernet port (GBE0) for use on a carrier board. Refer to the *Secondary Ethernet (GBE1)* section of Chapter 2, *User-Defined FPGA Signals*, for information about implementing a secondary Gigabit Ethernet port.

# **GBE0** Signal Definitions

Table 1-1 describes the GBE0 port pins and signals on the J1 connector on the sbRIO-9651 SOM.

| Signal Name                                                                                                          | Dedicated<br>SOM Pin #                    | Direction* | I/O<br>Standard                                 | Description                                     |

|----------------------------------------------------------------------------------------------------------------------|-------------------------------------------|------------|-------------------------------------------------|-------------------------------------------------|

| GBE0_MDI0_P<br>GBE0_MDI0_N<br>GBE0_MDI1_P<br>GBE0_MDI1_N<br>GBE0_MDI2_P<br>GBE0_MDI2_N<br>GBE0_MDI3_P<br>GBE0_MDI3_N | 1<br>9<br>18<br>26<br>3<br>11<br>20<br>28 | I/O        | Defined by<br>Ethernet<br>PHY<br>specification. | Pre-magnetic<br>Gigabit Ethernet<br>data pairs. |

| GBE0_SPEED_LEDg<br>GBE0_SPEED_LEDy                                                                                   | 5<br>13                                   | О          | LVTTL                                           | Speed LED signals.                              |

| GBE0_ACT_LEDg                                                                                                        | 6                                         | 0          | LVTTL                                           | Activity/link<br>LED signal.                    |

| * I/O direction is with respect to the sbRIO-9651 SOM.                                                               |                                           |            |                                                 |                                                 |

Table 1-1. GBE0 Signal Definitions

# GBE0 Implementation on the Reference Carrier Board

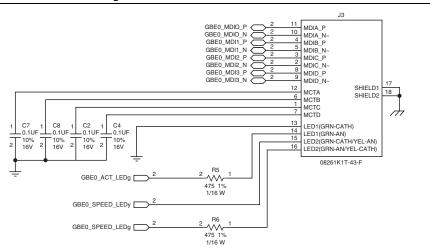

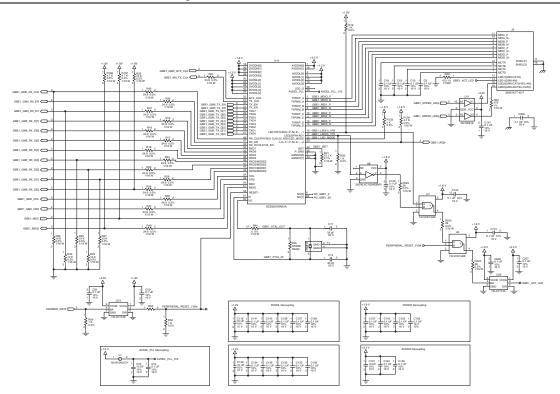

Figure 1-1 shows a schematic design for the GBE0 implementation on the reference carrier board.

#### **Reference Schematic Design Considerations**

Table 1-2 lists design considerations for the schematic shown in Figure 1-1.

| Consideration  | Notes                                                                                                                                                                                                        |  |  |  |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| MDI data pairs | • The MDI data pairs are routed differentially and connected directly to the Ethernet connector.                                                                                                             |  |  |  |

|                | • The Ethernet connector has the required Ethernet magnetics built into it. You may use discrete magnetics instead.                                                                                          |  |  |  |

| LED signals    | • The LED signals can be used to directly drive connector LEDs.                                                                                                                                              |  |  |  |

|                | • The current-limiting resistors must be sized so that the drive current of the LED signals is not exceeded.                                                                                                 |  |  |  |

|                | • Refer to the <i>Ethernet Speed LED Behavior</i> section of the <i>NI sbRIO-9651 System on Module OEM Device Specifications</i> for information about Ethernet LED signal behavior and rated drive current. |  |  |  |

# Gigabit Ethernet Magnetic Requirements

The Ethernet PHY on the sbRIO-9651 SOM uses voltage-mode drivers for the MDI pairs, which greatly reduces the power that the magnetics consume and eliminates the need for a sensitive center tap power supply.

You must consider the following requirements for connecting center taps:

- Do not connect the center taps of the isolation transformer on the MDI pair side to any power source. Keep the center taps separate from each other.

- Connect each center tap through separate 0.1 µF capacitors to ground. The separation is required because the common-mode voltage on each MDI pair might be different.

Table 1-3 lists recommended magnetic characteristics.

| Parameter                     | Value       | Test Condition       |

|-------------------------------|-------------|----------------------|

| Turns ratio                   | 1 CT : 1 CT | —                    |

| Open-circuit inductance (min) | 350 μH      | 100 mV, 100kHz, 8 mA |

| Insertion loss (max)          | 1.0 dB      | 0 MHz to 100 MHz     |

| HIPOT (min)                   | 1500 Vrms   | —                    |

Table 1-3. Recommended Magnetic Characteristics

The sbRIO-9651 SOM development kit uses the Gigabit Ethernet connector parts described in Table 1-4.

Table 1-4. Gigabit Ethernet Connector Parts

| Part                                                  | Manufacturer        | Part Number    |

|-------------------------------------------------------|---------------------|----------------|

| sbRIO-9651 SOM PHY                                    | Micrel              | KSZ9031MNXIA   |

| Reference carrier board Gigabit<br>Ethernet connector | Bel Stewart Magjack | 0826-1K1T-43-F |

Refer to the datasheet for the Micrel Ethernet PHY for more information about magnetic requirements.

# **GBE0** Routing Considerations

NI recommends the following design practices for properly routing GBE0 signals on your carrier board:

- Route MDI pairs differentially with  $100 \Omega$  differential trace impedance.

- Length-match the positive and negative signal for each MDI data pair to within 10 mils.

• Limit the MDI trace lengths on the carrier board to 6.0 in. or less, which is the length at which Ethernet compliance was tested.

# USB (USB0, USB1)

The sbRIO-9651 SOM provides two USB 2.0-compliant ports for use on a carrier board: USB Host/Device port (USB0) and USB Host port (USB1).

**Note** Your carrier board design must provide the 5 V USB\_VBUS power to USB Host ports and must limit the current supplied to each host port according to USB specifications.

# USB0 Host/Device Signal Definitions

Table 1-5 describes the USB0 Host/Device port pins and signals on the sbRIO-9651 SOM connector.

| Signal Name                                            | Dedicated<br>SOM Pin # | Direction* | I/O Standard                  | Description                                                                                                                                                                                  |  |  |

|--------------------------------------------------------|------------------------|------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| USB0_DP                                                | 33                     | I/O        | Defined by                    | USB0 data pair.                                                                                                                                                                              |  |  |

| USB0_DN                                                | 41                     |            | USB specification.            |                                                                                                                                                                                              |  |  |

| USB0_MODE                                              | 65                     | Ι          | LVTTL                         | Controls whether the<br>USB0 port provides a<br>Host or Device<br>connection. Refer to the<br><i>Configuring the USB0</i><br><i>Mode</i> section of this<br>chapter for more<br>information. |  |  |

| USB0_CPEN                                              | 73                     | 0          | LVTTL                         | USB0 over-current protection enable.                                                                                                                                                         |  |  |

| USB0_VBUS                                              | 81                     | Ι          | 5 V tolerant<br>voltage sense | USB0 VBUS input.<br>Allows USB PHY to<br>sense if VBUS is<br>present on the<br>connector.                                                                                                    |  |  |

| * I/O direction is with respect to the sbRIO-9651 SOM. |                        |            |                               |                                                                                                                                                                                              |  |  |

Table 1-5. USB0 Host/Device Signal Definitions

### Configuring the USB0 Mode

You can configure the USB0 interface to be a USB Host port or a USB Device port, as shown in Table 1-6. This mode is set when the system boots and does not change dynamically. The reference carrier board uses the USB0 interface for a USB Device port.

Note USB On-The-Go (OTG) is not supported.

| Mode       | How to Enable                                                                                                                                                                                                                                                                                                             |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| USB Host   | Connect the USB0_MODE signal to digital ground on your carrier<br>board. You can implement USB0 Host functionality in the same way that<br>the USB1 Host signal is implemented on the reference carrier board, as<br>described in the USB1 Host Implementation on the Reference Carrier<br>Board section of this chapter. |

| USB Device | Connect the USB0_MODE signal to the VCC_3V3 rail on your carrier board. Refer to the USB0 Device Implementation on the Reference Carrier Board section of this chapter for more information about the USB0 Device implementation on the reference carrier board.                                                          |

Table 1-6. Configuring the USB0 Mode

# USB0 Device Implementation on the Reference Carrier Board

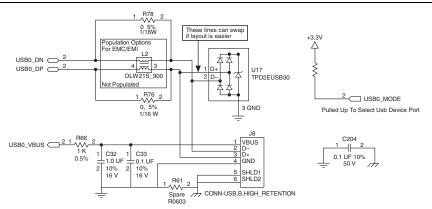

Figure 1-2 shows a schematic design for the USB0 Device implementation on the reference carrier board.

Figure 1-2. USB0 Device Reference Schematic

### **Reference Schematic Design Considerations**

Table 1-7 lists design considerations for the schematic shown in Figure 1-2.

| Consideration | Notes                                                                                                                                                                        |  |  |  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| USB data pair | • The USB0_DP and USB0_DN data pair is routed differentially to the USB connector.                                                                                           |  |  |  |

|               | • On the reference carrier board, the L2 common-mode choke is not populated, but you can populate it in your design to help with conducted immunity or emissions.            |  |  |  |

|               | • If you choose to populate L2, remove R76 and R78 from your design.                                                                                                         |  |  |  |

|               | <ul> <li>If your design does not include a common-mode choke, you can route<br/>the USB pair directly from the USB connector to the sbRIO-9651<br/>SOM connector.</li> </ul> |  |  |  |

|               | • U17 provides ESD protection to the USB data pair and should be placed close to the USB connector.                                                                          |  |  |  |

| USB0_MODE     | The USB0_MODE signal is pulled up to 3.3 V to select USB Device functionality.                                                                                               |  |  |  |

| USB0_CPEN     | Leave the USB0_CPEN signal disconnected for a USB Device port.                                                                                                               |  |  |  |

| USB0_VBUS     | • For the USB Device port to function properly, the USB0_VBUS signal must be connected to the VBUS pin on the USB connector.                                                 |  |  |  |

|               | • This is a low-current, voltage-sense connection.                                                                                                                           |  |  |  |

|               | • In layout, you can treat this connection as a data signal.                                                                                                                 |  |  |  |

|               | • R66 helps provide some overvoltage protection on USB0_VBUS and should be placed close to the USB connector. NI recommends that you use a 1 k $\Omega$ resistor.            |  |  |  |

| Table 1 7  |             | Deference | Sobomatia | Docian | Considerations |

|------------|-------------|-----------|-----------|--------|----------------|

| Table 1-7. | USED Device | neierence | Schematic | Design | Considerations |

# **USB1 Host Signal Definitions**

Table 1-8 describes the USB1 Host port pins and signals on the sbRIO-9651 SOM connector.

| Signal Name | Dedicated<br>SOM Pin # | Direction* | I/O<br>Standard    | Description     |

|-------------|------------------------|------------|--------------------|-----------------|

| USB1_DP     | 35                     | I/O        | Defined by         | USB1 data pair. |

| USB1_DN     | 43                     |            | USB specification. |                 |

Table 1-8. USB1 Host Signal Definitions

| Signal Name | Dedicated<br>SOM Pin # | Direction* | I/O<br>Standard               | Description                                                                            |

|-------------|------------------------|------------|-------------------------------|----------------------------------------------------------------------------------------|

| USB1_CPEN   | 50                     | 0          | LVTTL                         | USB1 over-current protection enable.                                                   |

| USB1_VBUS   | 58                     | Ι          | 5 V tolerant<br>voltage sense | USB1 VBUS input.<br>Allows USB PHY to<br>sense if VBUS is present<br>on the connector. |

Table 1-8. USB1 Host Signal Definitions (Continued)

USB1 Host Implementation on the Reference Carrier Board

Figure 1-3 shows a schematic design for the USB1 Host implementation on the reference carrier board.

Figure 1-3. USB1 Host Reference Schematic

#### **Reference Schematic Design Considerations**

Table 1-9 lists design considerations for the schematic shown in Figure 1-3.

| Consideration | Notes                                                                                                                                                                               |  |  |  |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| USB data pair | • The USB1_DP and USB1_DN data pair is routed differentially to the USB connector.                                                                                                  |  |  |  |

|               | • On the reference carrier board, the L3 common-mode choke is no populated, but you can populate it in your design to help with conducted immunity or emissions.                    |  |  |  |

|               | • If you choose to populate L3, remove R79 and R82 from your design.                                                                                                                |  |  |  |

|               | • If your design does not include a common-mode choke, you can route the USB pair directly from the USB connector to the sbRIO-9651 SOM connector.                                  |  |  |  |

|               | • U18 provides ESD protection to the USB data pair and should be placed close to the USB connector.                                                                                 |  |  |  |

| USB1_CPEN     | The USB1_CPEN signal must be connected to the enable of the VBUS current limit switch (U20). This allows the sbRIO-9651 SOM to power-cycle USB devices when the processor is reset. |  |  |  |

| USB1_VBUS     | • For the USB Host port to function properly, the USB1_VBUS signal must be connected to VBUS on the USB connector.                                                                  |  |  |  |

|               | • This is a low-current, voltage-sense connection.                                                                                                                                  |  |  |  |

|               | • In layout, you can treat the trace after R92 going to the sbRIO-9651 SOM connector as a data signal.                                                                              |  |  |  |

|               | • R92 helps provide some overvoltage protection on USB1_VBUS and should be placed close to the USB connector. NI recommends that you use a 1 k $\Omega$ resistor.                   |  |  |  |

|               | • The carrier board must provide 5 V VBUS power for the USB Host port.                                                                                                              |  |  |  |

|               | • A current limit switch is required between the 5 V rail and the USB connector.                                                                                                    |  |  |  |

|               | • U20 is the current limiter.                                                                                                                                                       |  |  |  |

|               | - NI recommends that you provide 100 $\mu F$ of capacitance on the VBUS rail.                                                                                                       |  |  |  |

Table 1-9. USB1 Host Reference Schematic Design Considerations

# Supporting Onboard USB Devices

When you implement a USB device directly on your carrier board, you can connect the device to a USB Host port from the sbRIO-9651 SOM. For this case, use the following design guidelines:

- You can connect the USB data pair directly to a USB device on your carrier board.

- A current limiter is not required.

- Use the CARRIER\_RST# signal to reset the USB device when the sbRIO-9651 SOM is in reset.

- Tie the USBx\_VBUS signal to 3.3 V or 5 V.

# **USB** Routing Considerations

NI recommends the following design practices for properly routing USB signals on your carrier board:

- Route the USBx\_DP and USBx\_DN signals as differential pairs with 90 Ω differential impedance.

- Length-match the positive and negative signal for each USB data pair to within 10 mils.

- Limit the USBx\_DP and USBx\_DN trace lengths on the carrier board to 8.0 in. or less, which is the length at which USB compliance was tested.

# UART/Console Out (Serial1)

The sbRIO-9651 SOM provides a dedicated UART (Serial1) interface for use on a carrier board. This interface also functions as an operating system console when Console Out is enabled. Refer to the *Additional RS-232 (Serial2, Serial3, Serial4)* and *RS-485 (Serial5, Serial6)* sections of Chapter 2, *User-Defined FPGA Signals*, for information about implementing additional serial ports.

# Serial1 Signal Definitions

Table 1-10 describes the Serial1 port pins and signals on the sbRIO-9651 SOM connector.

**Note** The NI-Serial driver has been developed for and tested with the Texas Instruments TRS3253EIRSMR RS-232 transceiver. Other transceivers may be compatible.

| Signal Name                                            | Dedicated<br>SOM Pin # | Direction* | I/O<br>Standard | Description                                 |  |  |

|--------------------------------------------------------|------------------------|------------|-----------------|---------------------------------------------|--|--|

| SERIAL1_TX                                             | 52                     | 0          | LVTTL           | Two-wire serial and                         |  |  |

| SERIAL1_RX                                             | 60                     | Ι          |                 | console out signals for the sbRIO-9651 SOM. |  |  |

| * I/O direction is with respect to the sbRIO-9651 SOM. |                        |            |                 |                                             |  |  |

Table 1-10. Serial1 Signal Definitions

### Serial1 Implementation on the Reference Carrier Board

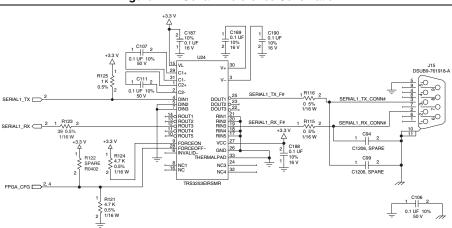

Figure 1-4 shows a schematic design for the Serial1 implementation on the reference carrier board.

### **Reference Schematic Design Considerations**

Table 1-11 lists design considerations for the schematic shown in Figure 1-4.

| Consideration         | Notes                                                                                                                                                                                                                      |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Interface             | The reference carrier board demonstrates how to use the Serial1 interface to implement a two-wire RS-232 serial port.                                                                                                      |

| Serial<br>transceiver | U24 is the RS-232 serial transceiver that converts between RS-232 and LVTTL signal levels. To minimize the impact of higher voltage signals on your carrier board, place the serial transceiver near the RS-232 connector. |

| Consideration         | Notes                                                                                                                                                                                                                                                                 |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Series<br>termination | R123 is the series termination for SERIAL1_RX. Use series termination<br>at the serial transceiver on all signals being driven to the sbRIO-9651<br>SOM. The sbRIO-9651 SOM provides onboard series termination for<br>SERIAL1_TX near the Xilinx Zynq SoC.           |

| FPGA                  | All serial port signals pass through the FPGA on the sbRIO-9651 SOM.<br>The FPGA_CFG signal is used to disable the serial transceiver when the<br>FPGA is not configured. Disabling the transceiver in this way prevents<br>any unwanted glitches on the RS-232 port. |

## Adding Flow Control and Modem Control Signals

You can use the sbRIO CLIP Generator application included with the NI-RIO Device Drivers software to add optional flow control and modem control signals to the Serial1 interface.

Refer to the *Additional RS-232 (Serial2, Serial3, Serial4)* section of Chapter 2, *User-Defined FPGA Signals*, for an example of how to implement a full-modem RS-232 port. Refer to the *NI Single-Board RIO CLIP Generator Help*, described in the *Additional Documentation Resources* section of the *About This Document* preface, for more information about using the sbRIO CLIP Generator application.

# SD Card

The sbRIO-9651 SOM provides a Secure Digital (SD) Card interface for use on a carrier board. This interface supports SD and SDHC cards. You can implement this interface with standard SD or microSD card connectors. The maximum supported SDHC card capacity is 32 GB.

# **SD Signal Definitions**

Table 1-12 describes the SD pins and signals on the sbRIO-9651 SOM connector.

| Signal Name                                            | Dedicated<br>SOM Pin # | Direction* | I/O Standard | Description                                                                                                                  |

|--------------------------------------------------------|------------------------|------------|--------------|------------------------------------------------------------------------------------------------------------------------------|

| SD_CLK                                                 | 15                     | 0          | LVTTL        | SD clock.                                                                                                                    |

| SD_CMD                                                 | 31                     | I/O        | LVTTL        | SD command.                                                                                                                  |

| SD_D0<br>SD_D1<br>SD_D2<br>SD_D3                       | 8<br>22<br>24<br>30    | I/O        | LVTTL        | SD data bus.                                                                                                                 |

| SD_CD#                                                 | 32                     | Ι          | LVTTL        | SD card detect.<br>Assert low when<br>card is present.<br>Can connect to a<br>mechanical switch in<br>the SD card socket.    |

| SD_WP                                                  | 40                     | Ι          | LVTTL        | SD write protect.<br>Assert high to enable<br>protection. Can<br>connect to a<br>mechanical switch in<br>the SD card socket. |

| SD_PWR_EN                                              | 38                     | 0          | LVTTL        | Power enable for SD card socket.                                                                                             |

| * I/O direction is with respect to the sbRIO-9651 SOM. |                        |            |              |                                                                                                                              |

Table 1-12. SD Signal Definitions

### SD Implementation on the Reference Carrier Board

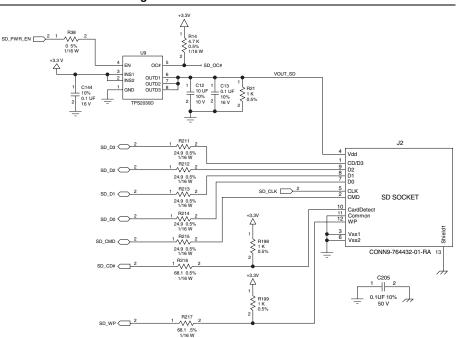

Figure 1-5 shows a schematic design for the SD implementation on the reference carrier board.

Figure 1-5. SD Reference Schematic

#### **Reference Schematic Design Considerations**

Table 1-13 lists design considerations for the schematic shown in Figure 1-5.

| Consideration          | Notes                                                                                                                                                                                                                                                                                                          |  |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SD_CLK,<br>SD_CMD, and | • You can route these signals directly from the sbRIO-9651 SOM to the SD connector.                                                                                                                                                                                                                            |  |

| SD_D0 through<br>SD_D3 | • Each of these signals requires series termination near its driver. The sbRIO-9651 SOM provides series termination near the Xilinx Zynq SoC to prevent overshoot on the SD card when the sbRIO-9651 SOM drives these signals. The bi-directional signals also require series termination at the SD converter. |  |

|                        | • Use series termination at the SD connector for the SD_CMD and SD_D0 through SD_D3 signals to prevent overshoot on the sbRIO-9651 SOM when the SD card drives these signals.                                                                                                                                  |  |

| SD_CD#                 | • The SD_CD# signal is connected to the mechanical card-detect switch in the SD connector.                                                                                                                                                                                                                     |  |

|                        | • When a card is inserted, the card-detect pin on the SD connector is shorted to ground.                                                                                                                                                                                                                       |  |

|                        | • Because this is a mechanical switch with low output impedance, you must place a series termination resistor (R216) at the SD connector.                                                                                                                                                                      |  |

|                        | • You must have a card-detect switch to properly support hot-swapping cards. If you do not need to support hot-swapping cards, you can use an SD connector without a card-detect switch. In this case, tie the SD_CD# signal to ground so that the sbRIO-9651 SOM attempts to initialize a card on boot.       |  |

Table 1-13. SD Reference Schematic Design Considerations

| Consideration | Notes                                                                                                                                                                                       |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SD_WP         | • When the SD_WP signal is asserted high, the sbRIO-9651 will not write to the SD card.                                                                                                     |

|               | • Standard-size SD card connectors provide a mechanical write-protect switch that you can connect to the SD_WP signal. The switch detects the position of the lock slide on the SD card.    |

|               | • Because this is a mechanical switch with low output impedance, you must place a series termination resistor (R217) at the SD connector.                                                   |

|               | • If you are using a microSD connector or do not have a write-protect switch, you can tie the SD_WP signal to ground in order to disable write protection and allow changes to the SD card. |

| SD_PWR_EN     | • Use the SD_PWR_EN signal to gate power to the SD connector.                                                                                                                               |

|               | • U9 acts as a power switch and current limiter for the SD interface.<br>SDHC cards must not draw more than 200 mA.                                                                         |

|               | • The SD_PWR_EN signal controls when power is going to the SD card.                                                                                                                         |

|               | • The SD_PWR_EN signal asserts high when a card is detected using the SD_CD# signal. The SD_PWR_EN signal deasserts when a card is not present.                                             |

Table 1-13. SD Reference Schematic Design Considerations (Continued)

# SD Routing Considerations

NI recommends the following design practices for properly routing SD signals on your carrier board:

- Length-match the SD\_CMD and SD\_D0 through SD\_D3 signals to within ±250 mils of SD\_CLK.

- Limit the trace length of the SD\_CLK, SD\_CMD, and SD\_D0 through SD\_D3 signals on the carrier board to 8.0 in. or less.

# RTC Battery (VBAT)

The reference carrier board contains a lithium cell battery that maintains the real-time clock (RTC) on the sbRIO-9651 SOM when the sbRIO-9651 SOM is powered off. A slight drain on the battery occurs when power is not applied to the sbRIO-9651 SOM. For information about the VBAT current drain, refer to the *VBAT Requirements* section of the *NI sbRIO-9651 System on Module OEM Device Specifications*.

If the battery is dead, or if no voltage has been applied to the VBAT pins, the system still starts but the system clock resets to the UNIX epoch date and time.

# **VBAT** Signal Definitions

Table 1-14 describes the VBAT pins and signals on the sbRIO-9651 SOM connector.

| Signal Name | Dedicated<br>SOM Pin # | Direction* | I/O<br>Standard | Description                                                                                      |  |

|-------------|------------------------|------------|-----------------|--------------------------------------------------------------------------------------------------|--|

| VBAT        | 64                     | Ι          | Power rail      | RTC battery input that<br>provides backup power to<br>the RTC to keep track of<br>absolute time. |  |

| *           |                        |            |                 |                                                                                                  |  |

Table 1-14. VBAT Signal Definitions

# VBAT Implementation on the Reference Carrier Board

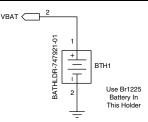

Figure 1-6 shows a schematic design for the VBAT implementation on the reference carrier board.

### **Reference Schematic Design Considerations**

You can directly connect the battery to VBAT. The sbRIO-9651 SOM already provides a current-limiting resistor and reverse-voltage protection.

# Eliminating the Effects of Contact Bounce

If you are using the A revision of the sbRIO-9651 SOM, it is important to eliminate the effects of contact bounce when you initially attach the battery.

**Note** To determine the revision, check the bottom side of the sbRIO-9651 SOM for a sticker with the part number 157660x-01L, where *x* is the revision letter.

Contact bounce can cause a momentary power interruption to the RTC, which might result in drift greater than the RTC accuracy listed in the *NI sbRIO-9651 System on Module OEM Device Specifications*.

To eliminate the effects of contact bounce, try one of the following methods:

- (Preferred) Use power sequencing by applying Vcc to the RTC before attaching the battery.

- Filter the signal using a small capacitor between VBAT and ground. The manufacturer recommends capacitor values between 0.1 nf and 1.0 nf.

# Resets

The sbRIO-9651 SOM provides signals for implementing a reset button on a carrier board and indicating that the sbRIO-9651 SOM is in reset.

# **Reset Signal Definitions**

Table 1-15 describes the Reset pins and signals on the sbRIO-9651 SOM connector.

| Signal Name                                            | Dedicated<br>SOM Pin # | Direction* | I/O<br>Standard | Description                                                                                                            |

|--------------------------------------------------------|------------------------|------------|-----------------|------------------------------------------------------------------------------------------------------------------------|

| CARRIER_RST#                                           | 37                     | 0          | LVTTL           | Reset that indicates that<br>main power is not<br>adequate or that the<br>sbRIO-9651 SOM is in<br>reset. Asserted low. |

| SYS_RST#                                               | 47                     | Ι          | LVTTL           | System reset that puts<br>the sbRIO-9651 SOM<br>in reset. Asserted low.                                                |

|                                                        |                        |            |                 | Asserting this signal<br>causes the<br>CARRIER_RST#<br>signal to also assert.                                          |

|                                                        |                        |            |                 | You can also assert this<br>signal to put the<br>sbRIO-9651 SOM into<br>safe mode or reset<br>IP address settings.     |

| * I/O direction is with respect to the sbRIO-9651 SOM. |                        |            |                 |                                                                                                                        |

| Table 1-15. | Reset Signal | Definitions |

|-------------|--------------|-------------|

|-------------|--------------|-------------|

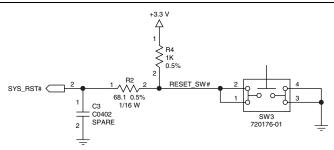

# Reset Implementation on the Reference Carrier Board

Figure 1-7 shows a schematic design for the Reset implementation on the reference carrier board.

Refer to the SYS\_RST# and CARRIER\_RST# sections of the NI sbRIO-9651 System on Module OEM Device Specifications for more information about the behavior of the Reset signals.

#### **Reference Schematic Design Considerations**

Table 1-16 lists design considerations for the schematic shown in Figure 1-7.

| Consideration         | Notes                                                                                                                                                                                                                                   |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Series<br>termination | When SYS_RST# is driven, you must place a series termination resistor<br>at the driver. When the driver is a mechanical switch, placing series<br>termination is especially important due to the low output impedance of<br>the switch. |

Table 1-16. Reset Reference Schematic Design Considerations

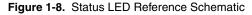

# Status LED

The sbRIO-9651 SOM provides a Status LED signal for use on a carrier board. The Status LED indicates the status of the SOM boot process or Safe Mode and can be used to report software errors.

# Status LED Signal Definitions

Table 1-17 describes the Status LED pins and signals on the sbRIO-9651 SOM connector.

| Signal Name                                            | Dedicated<br>SOM Pin # | Direction* | I/O<br>Standard | Description           |

|--------------------------------------------------------|------------------------|------------|-----------------|-----------------------|

| STATUS_LED                                             | 14                     | 0          | LVTTL           | Status LED indicator. |

| * I/O direction is with respect to the sbRIO-9651 SOM. |                        |            |                 |                       |

| Table 1-17. | Status LED Signal Definitions |

|-------------|-------------------------------|

|-------------|-------------------------------|

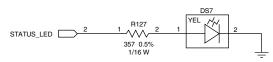

# Status LED Implementation on the Reference Carrier Board

Figure 1-8 shows a schematic design for the Status LED implementation on the reference carrier board.

Refer to the *STATUS\_LED* section of the *NI sbRIO-9651 System on Module OEM Device Specifications* for more information about the behavior of the Status LED signal.

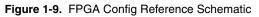

# **FPGA** Config

The sbRIO-9651 SOM provides an FPGA Config signal to indicate when the FPGA is configured.

# FPGA Config Signal Definitions

Table 1-18 describes the FPGA Config pins and signals on the sbRIO-9651 SOM connector.

| Signal<br>Name | Dedicated<br>SOM Pin # | Direction* | I/O Standard                                                                                                                                       | Description                                                                                                      |

|----------------|------------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| FPGA_CFG       | 53                     | 0          | Refer to the<br>NI sbRIO-9651<br>System on Module<br>OEM Device<br>Specifications for<br>more information<br>about the behavior<br>of this signal. | FPGA Config Asserts<br>when the FPGA is<br>configured. Asserted<br>high when the FPGA<br>has been<br>programmed. |

Table 1-18. FPGA Config Signal Definitions

\* I/O direction is with respect to the sbRIO-9651 SOM.

# FPGA Config Implementation on the Reference Carrier Board

Figure 1-9 shows a schematic design for the FPGA Config implementation on the reference carrier board.

Refer to the *FPGA\_CFG* section of the *NI sbRIO-9651 System on Module OEM Device Specifications* for more information about the behavior of the FPGA Config signal.

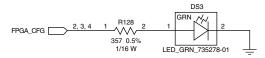

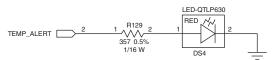

# Temp Alert

The sbRIO-9651 SOM provides a Temp Alert signal to indicate that the onboard CPU/FPGA or Primary System temperature has exceeded the minimum or maximum temperature specifications of the sbRIO-9651 SOM. Refer to the *Environmental* section of the *NI sbRIO-9651 System on Module OEM Device Specifications* for the minimum and maximum temperature specifications.

## Temp Alert Signal Definitions

Table 1-19 describes the Temp Alert pins and signals on the sbRIO-9651 SOM connector.

| Signal Name                                            | Dedicated<br>SOM Pin # | Direction* | I/O<br>Standard | Description                             |

|--------------------------------------------------------|------------------------|------------|-----------------|-----------------------------------------|

| TEMP_ALERT                                             | 46                     | 0          | LVTTL           | Temp Alert indicator.<br>Asserted high. |

| * I/O direction is with respect to the sbRIO-9651 SOM. |                        |            |                 |                                         |

Table 1-19. Temp Alert Signal Definitions

# Temp Alert Implementation on the Reference Carrier Board

Figure 1-10 shows a schematic design for the Temp Alert implementation on the reference carrier board.

#### Figure 1-10. Temp Alert Reference Schematic

Refer to the *TEMP\_ALERT* section of the *NI sbRIO-9651 System on Module OEM Device Specifications* for more information about the behavior of the Temp Alert signal.

Refer to the *Validating Temperature Measurements* section of Chapter 4, *Mechanical Considerations*, for information about validating the system temperatures of your sbRIO-9651 SOM application.

# 2

# **User-Defined FPGA Signals**

The sbRIO-9651 SOM connector provides several banks of FPGA pins that you can configure for purposes specific to your application. In addition to FPGA Digital I/O (DIO), you can use these pins to implement the following run-time peripheral interfaces:

- Secondary Ethernet (GBE1)

- Additional RS-232 (Serial2, Serial3, Serial4)

- RS-485 (Serial5, Serial6)

- CAN (CAN0, CAN1)

The reference carrier board included with the sbRIO-9651 SOM development kit shows an example of how to implement these signals. Refer to the specific sections in this chapter for more information about how the reference carrier board implements each signal.

**Note** To read or write to this I/O from a LabVIEW project, you must use the sbRIO CLIP Generator application to create a socketed component-level IP (CLIP) that defines the I/O configuration of the sbRIO-9651 SOM to use in your application. Refer to the *Getting Started with the NI sbRIO-9651 in LabVIEW* topic in the *LabVIEW Help* for more information about creating a CLIP.

**Tip** When you create your own CLIP, you must compile your FPGA VI and download it to the flash of the sbRIO-9651 SOM. This ensures that the driver for each enabled peripheral can load properly at boot time. Refer to the *Downloading an FPGA VI to the Flash Memory of an FPGA Target* topic in the *LabVIEW Help* (*FPGA Module*) for more information.

# Secondary Ethernet (GBE1)

You must use specific FPGA pins to implement a secondary Ethernet port due to the strict timing requirements across semiconductor process and temperature variations.

The reference carrier board implements one secondary Ethernet port (GBE1) in addition to the primary Ethernet port. Refer to the *Primary Ethernet (GBE0)* section of Chapter 1, *Fixed Behavior Signals*, for more information about implementing a primary Ethernet port.

**Note** The sbRIO CLIP Generator enforces the selection of specific FPGA pins when you implement a secondary Ethernet port.

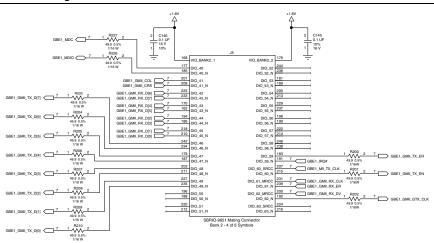

# GBE1 Signal Definitions on the Reference Carrier Board

Table 2-1 describes the GBE1 pins and signals on the sbRIO-9651 SOM connector used to implement a secondary Ethernet port on the reference carrier board.

|                                                                                                                                                      |                                                      | r                                                                                    | 1          |                        |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--------------------------------------------------------------------------------------|------------|------------------------|--|

| Signal Name                                                                                                                                          | Pin #*                                               | DIO Signal on<br>Reference<br>Carrier Board                                          | Direction† | Description            |  |

| TX Signals                                                                                                                                           |                                                      |                                                                                      |            |                        |  |

| GBE1_GMII_GTX_CLK                                                                                                                                    | 192                                                  | DIO_62_N                                                                             | 0          | Gigabittransmit clock. |  |

| GBE1_MII_TX_CLK                                                                                                                                      | 207                                                  | DIO_60_SRCC                                                                          | Ι          | 10/100 transmit clock. |  |

| GBE1_GMII_TX_EN                                                                                                                                      | 215                                                  | DIO_60_N                                                                             | О          | Transmit<br>enable.    |  |

| GBE1_GMII_TX_ER                                                                                                                                      | 183                                                  | DIO_59                                                                               | 0          | Transmit error.        |  |

| GBE1_GMII_TX_D0<br>GBE1_GMII_TX_D1<br>GBE1_GMII_TX_D2<br>GBE1_GMII_TX_D3<br>GBE1_GMII_TX_D4<br>GBE1_GMII_TX_D5<br>GBE1_GMII_TX_D6<br>GBE1_GMII_TX_D7 | 235<br>227<br>211<br>203<br>187<br>179<br>234<br>242 | DIO_49_N<br>DIO_49<br>DIO_48_N<br>DIO_48<br>DIO_47_N<br>DIO_47<br>DIO_46_N<br>DIO_46 | 0          | Transmit data<br>bus.  |  |

| RX Signals                                                                                                                                           |                                                      |                                                                                      |            |                        |  |