# **PXIe-5622**

# **Contents**

| PXIe-5622 Specifications | 3 |

|--------------------------|---|

|                          |   |

# PXIe-5622 Specifications

These specifications apply to the PXIe-5622 with 64 MB and 256 MB of memory.

Hot Surface If the PXIe-5622 has been in use, it may exceed safe handling temperatures and cause burns. Allow the PXIe-5622 to cool before removing it from the chassis.

Caution Do not operate the PXIe-5622 in a manner not specified in this document. Product misuse can result in a hazard. You can compromise the safety protection built into the product if the product is damaged in any way. If the product is damaged, return it to NI for repair.

#### **Definitions and Conditions**

Specifications are subject to change without notice. For the most recent PXIe-5622 specifications, visit <u>ni.com/manuals</u>. Unless otherwise noted, the following conditions were used for each specification:

- Direct path filter setting enabled

- Sample clock set to internal 150 MS/s, unlocked

- 1 V vertical range

**Specifications** describe the warranted, traceable performance of the device over an ambient temperature range of 0 °C to 55 °C and include guardband for measurement uncertainty, unless otherwise noted. Specifications are valid under the following conditions unless otherwise noted:

- The PXIe-5622 module is warmed up for 15 minutes at ambient temperature.

- Calibration cycle is maintained.

- NI-SCOPE self-calibration performed after device temperature is stable.

- The PXI Express chassis fan speed is set to HIGH, the foam fan filters are removed if present, and the empty slots contain PXI chassis slot blockers and filler panels. For

more information about cooling, refer to the *Maintain Forced-Air Cooling Note to Users* available at ni.com/manuals.

• External calibration is performed at 23 °C ± 3 °C.

**Typical Specifications** are unwarranted values that describe the expected performance of the device over ambient temperature ranges of 23  $^{\circ}$ C  $\pm$  5  $^{\circ}$ C with a 90% confidence level.

**Characteristics** (or supplemental information) describe basic functions and attributes of the device established by design.

Data in this document are Specifications unless otherwise noted.

To access PXIe-5622 documentation, including the *PXIe-5622 Getting Started Guide*, go to Start » All Programs » National Instruments » NI-SCOPE » NI-SCOPE Documentation.

#### **Vertical**

#### Analog Input (IF IN)

| Number of channels                                          | One (IF IN)                                  |

|-------------------------------------------------------------|----------------------------------------------|

| Input impedance                                             | 50 $\Omega$ , characteristic                 |

| Input return loss                                           | <-15 dB, 5 MHz to 300 MHz, typical           |

| Input coupling                                              | AC, GND                                      |

| Full scale (FS) input voltage range (Vpk-pk) <sup>[1]</sup> | 0.7 V (+1 dBm), 1 V (+4 dBm), 1.4 V (+7 dBm) |

| Maximum voltage input overload (Vpk-pk) | 6.3 V (+20 dBm) |

|-----------------------------------------|-----------------|

|-----------------------------------------|-----------------|

#### **Accuracy**

| Resolution                                                                                           | 16-b     | 16-bit  |                                         |

|------------------------------------------------------------------------------------------------------|----------|---------|-----------------------------------------|

| Absolute amplitude accuracy, at center frequency of speci-                                           | fied bar | ıds, va | lid for all input ranges <sup>[2]</sup> |

| Bandpass Path (187.5 MHz)                                                                            |          |         | <±0.5 dB                                |

| Direct Path (53 MHz)                                                                                 |          |         | <±0.4 dB                                |

| Absolute amplitude accuracy, at center frequency of speci                                            | fied bar | ıds, va | lid for all input ranges <sup>[3]</sup> |

| Bandpass Path (187.5 MHz) <±0.3 dB,                                                                  |          | lB, typ | ical                                    |

| Direct Path (53 MHz) <±0.25 dB,                                                                      |          | dB, ty  | pical                                   |

| Temperature stability, maximum drift of ±2 °C from last self-calibration, valid for all input ranges |          |         |                                         |

| Bandpass Path (187.5 MHz)                                                                            |          | <0.0    | 1 dB/°C                                 |

| Direct Path (53 MHz)                                                                                 |          | <0.0    | 2 dB/°C                                 |

# Absolute Amplitude Accuracy Examples at 40 °C in the **Bandpass Path**

Amplitude accuracy specification:  $0.5 + 0.01 \times (40 - 23) = \pm 0.67 \text{ dB}$

Amplitude accuracy, typical:  $0.3 + 0.01 \times (40 - 23) = \pm 0.47 \text{ dB}$

# **Bandwidth and Frequency Response**

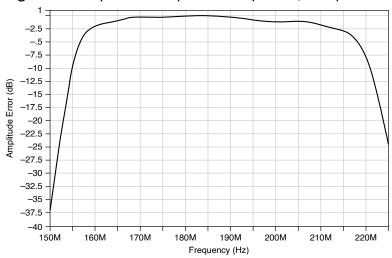

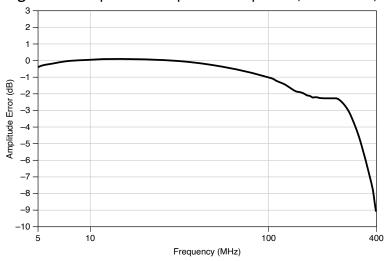

| Bandwidth (-3 dB), bandwidth of unequalized response                               |  |  |  |

|------------------------------------------------------------------------------------|--|--|--|

| Bandpass path (187.5 MHz) 50 MHz, centered at 187.5 MHz, 3rd Nyquist zone, typical |  |  |  |

| Direct path (53 MHz) 3 MHz to 250 MHz, typical                                     |  |  |  |

| Dither signal, frequency range <sup>[4]</sup> 100 kHz to 12 MHz, typical           |  |  |  |

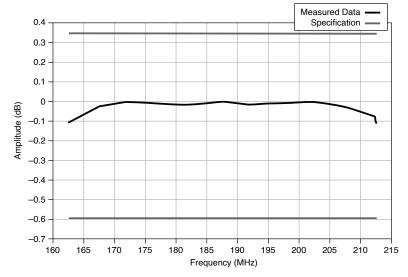

Figure 1. Equalized Amplitude Response (Bandpass Path), Using Calibration Data

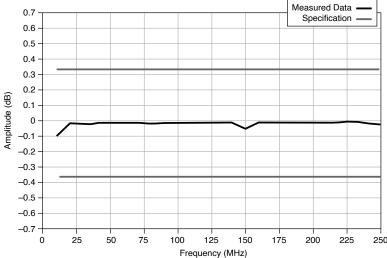

Figure 2. Equalized Amplitude Response (Direct Path), Using Calibration Data

Note The Direct Path Equalized Amplitude Response shown above is a composite plot of multiple segments of 40 MHz span each.

Figure 3. Unequalized Amplitude Response (Bandpass Path)

Figure 4. Unequalized Amplitude Response (Direct Path)

Table 1. Passband Amplitude Flatness

| Bandpass Path  Direct Path                                    |                                                                            |                                                                                                                                                     |

|---------------------------------------------------------------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                               | Daliupass Patti                                                            | Direct Patil                                                                                                                                        |

|                                                               | 187.5 MHz ±25 MHz                                                          | <±0.35 dB (equalized) 53 MHz ± 19 MHz                                                                                                               |

| Passband amplitude flatness, valid for 1 V range              |                                                                            | < ±0.6 dB (equalized)  10 MHz to 250 MHz (referenced to 100 MHz)                                                                                    |

| Passband amplitude flatness,<br>valid for all ranges, typical | <+0.25, -0.4 dB (equalized) <+0.7, -3.5 dB (unequalized) 187.5 MHz ±25 MHz | < ±0.25 dB (equalized) < ±0.6 dB (unequalized)  53 MHz ±19 MHz  <±0.5 dB (equalized)  <±1.8 dB (unequalized)  10 to 250 MHz (referenced to 100 MHz) |

Table 2. Passband phase linearity, valid for all input ranges, after equalization, typical

| Bandwidth | Bandpass Path Phase | Direct Path Phase |  |

|-----------|---------------------|-------------------|--|

| 10 MHz    | ±0.5°               | ±0.5°             |  |

| 20 MHz    | ±1°                 | ±1°               |  |

| 40 MHz    | ±1.75°              | n/a               |  |

| 50 MHz    | ±2.5°               |                   |  |

# **Spectral Characteristics** [6]

| Spurious-free dynamic range with harmonics (SFDR), for input signal with levels from -1 dBFS to -10 dBFS |                     |  |  |

|----------------------------------------------------------------------------------------------------------|---------------------|--|--|

| Bandpass path (187.5 MHz)                                                                                | <-76.5 dBc, typical |  |  |

| Direct path (53 MHz)                                                                                     | <-73 dBc, typical   |  |  |

| Total harmonic distortion (THD), includes 2nd through 5th                                                | harmonics           |  |  |

| Bandpass path (187.5 MHz)                                                                                | <-76 dBc, typical   |  |  |

| Direct path (53 MHz)                                                                                     | <-71 dBc, typical   |  |  |

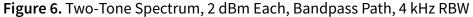

| Intermodulation distortion (IMD), two tones 1 MHz apart, down to -10 dBFS level                          |                     |  |  |

| Bandpass path (187.5 MHz)                                                                                | <-74 dBc, typical   |  |  |

| Direct path (53 MHz)                                                                                     | <-73 dBc, typical   |  |  |

Figure 5. Single Tone Spectrum, 5.5 dBm, Bandpass Path, 4 kHz RBW

Frequency (MHz)

#### Noise

| Full bandwidth Signal-to-Noise Ratio (SNR), internal VCXO at 150 MS/s |                   |  |  |

|-----------------------------------------------------------------------|-------------------|--|--|

| Bandpass path (187.5 MHz)                                             | >66.5 dB, typical |  |  |

| Direct path (53 MHz)                                                  | >67 dB, typical   |  |  |

| 4.28 MHz bandwidth SNR, DDC enabled, at 5.35 MS/s sample rate         |                   |  |  |

| Bandpass path (187.5 MHz)                                             | >71.5 dB, typical |  |  |

| Direct path (53 MHz) | >73 dB, typical |

|----------------------|-----------------|

|----------------------|-----------------|

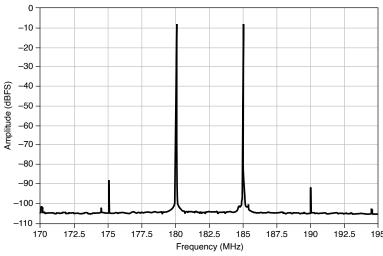

Table 3. SSB Phase Noise, Internal VCXO, Unlocked

|                          | Bandwidth        | Bandpass path<br>(187.5 MHz) | Direct path (53 MHz) |

|--------------------------|------------------|------------------------------|----------------------|

|                          | 100 Hz           | <-80 dBc/Hz                  | <-90 dBc/Hz          |

| SSB phase noise          | 1 kHz            | <-117 dBc/Hz                 | <-128 dBc/Hz         |

|                          | 10 kHz and above | <-134 dBc/Hz                 | <-141 dBc/Hz         |

|                          | 100 Hz           | <-83 dBc/Hz                  | <-94 dBc/Hz          |

| SSB phase noise, typical | 1 kHz            | <-120 dBc/Hz                 | <-132 dBc/Hz         |

| gp.ca.                   | 10 kHz and above | <-140 dBc/Hz                 | <-144 dBc/Hz         |

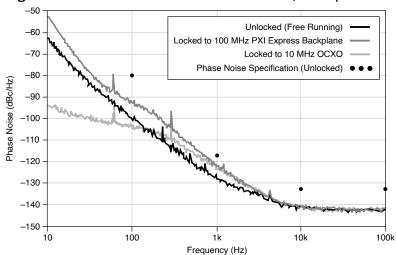

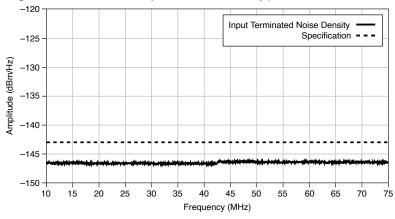

**Table 4.** Average noise density

|                                      | Range        | Value        |

|--------------------------------------|--------------|--------------|

|                                      | 0.7 V/+1 dBm | <-146 dBm/Hz |

| Average noise density <sup>[7]</sup> | 1 V/+4 dBm   | <-143 dBm/Hz |

|                                      | 1.4 V/+7 dBm | <-140 dBm/Hz |

| Average noise density, typical [8]   | 0.7 V/+1 dBm | <-149 dBm/Hz |

|                                      | 1 V/+4 dBm   | <-146 dBm/Hz |

|                                      | 1.4 V/+7 dBm | <-143 dBm/Hz |

Figure 7. Measured Phase Noise at 187 MHz, Bandpass Path, Signal Level = 3 dBm, Typical

## Horizontal

## Sample Clock

| Sample clock sources |                                                           |

|----------------------|-----------------------------------------------------------|

| Internal             | VCXO (can be free running or locked to a reference clock) |

| External             | CLK IN (front panel connector)                            |

## Onboard Clock (Internal VCXO)

| Sample rate <sup>[9]</sup>                                                | 150 MS/s with decimation by <b>N</b> |  |

|---------------------------------------------------------------------------|--------------------------------------|--|

| Accuracy                                                                  | $\pm 5.0 \times 10^{-6}$ , typical   |  |

| Accuracy over temperature                                                 | $\pm 12 \times 10^{-6}$ , typical    |  |

| SSB phase noise of 150 MHz Sample Clock when exported to CLK $OUT^{[10]}$ |                                      |  |

| 100 Hz                                                                    | <-90 dBc/Hz, typical                 |  |

| 1 kHz                                                                     | <-130 dBc/Hz, typical                |  |

| 10 kHz                                                                    | <-140 dBc/Hz, typical                |  |

| 100 kHz and above                                                         | <-150 dBc/Hz, typical                |  |

## Phase-Locked Loop (PLL) External Reference Clock

| Reference Clock sources (used to phase lock onboard VCXO)                        | CLK IN (front panel connector), PXIe<br>100 MHz (PXIe backplane) |

|----------------------------------------------------------------------------------|------------------------------------------------------------------|

| Sample Clock delay range (delay relative to Reference Clock when VCXO is locked) | ±1 Sample Clock period                                           |

| Sample Clock delay resolution (delay relative to                                 | ≤4 ps                                                            |

| Reference Clock when VCXO is locked)    |                                       |

|-----------------------------------------|---------------------------------------|

| Reference Clock frequency range         | 1 MHz to 100 MHz, in 1 MHz increments |

| Reference Clock frequency accuracy [11] | ±25 × 10 <sup>-6</sup>                |

| Reference Clock duty cycle tolerance    | 45% to 55%, typical                   |

| Reference Clock export ports            | CLK OUT (front panel connector)       |

# **External Sample Clock**

| Frequency range      | 20 MHz to 150 MHz               |

|----------------------|---------------------------------|

| Duty cycle tolerance | 45% to 55%, typical             |

| Export ports         | CLK OUT (front panel connector) |

# CLK IN (Sample Clock and Reference Clock Input, Front Panel Connector)

| Input impedance | 50 Ω, typical |

|-----------------|---------------|

| Coupling        | AC            |

| Amplitude       |               |

| Sine wave (Vpk-pk)              | 0.63 V to 2.8 V (0 to +13 | dBm)            |

|---------------------------------|---------------------------|-----------------|

| Square wave (Vpk-pk)            | 0.25 V to 2.8 V           |                 |

| Maximum input overload (Vpk-pk) |                           | 6.3 V (+20 dBm) |

## **CLK OUT (Sample Clock and Reference Clock Output, Front Panel Connector)**

| Output impedance                |    | 50 Ω, typical     |  |

|---------------------------------|----|-------------------|--|

| Coupling                        | AC |                   |  |

| Amplitude                       |    |                   |  |

| 50 Ω load                       |    | >+10 dBm, typical |  |

| 1 kΩ load, square wave (Vpk-pk) |    | > 2 V, typical    |  |

## **PFI 1 (Programmable Function Interface)**

| PFI 1 (programmable function interface) direction | Bi-directional |

|---------------------------------------------------|----------------|

|                                                   |                |

# Trigger

| Trigger types | Digital |  |

|---------------|---------|--|

|---------------|---------|--|

| As an input (trigger)  |                                                                                                  |  |

|------------------------|--------------------------------------------------------------------------------------------------|--|

| Destinations           | Start Trigger (Acquisition Arm) Reference (Stop) Trigger Arm Reference Trigger Advance Trigger   |  |

| Input impedance        | 150 kΩ, characteristic                                                                           |  |

| Range                  | 0 to 5 V, TTL compatible                                                                         |  |

| Maximum input overload | -3.5 V to +8 V, continuous                                                                       |  |

| Maximum frequency      | 20 MHz                                                                                           |  |

| Minimum trigger width  | >25 ns                                                                                           |  |

| As an output (event)   |                                                                                                  |  |

| Sources                | Start Trigger (Acquisition Arm) Reference (Stop) Trigger End of Record Done (End of Acquisition) |  |

| Output impedance       | 50 Ω, characteristic                                                                             |  |

| Logic type            | 3.3 V LVTTL |

|-----------------------|-------------|

| Maximum drive current | ±12 mA      |

| Maximum frequency     | 25 MHz      |

## **TClk Specifications**

You can use the NI TClk synchronization method and the NI-TClk driver to align the Sample clocks on any number of supported devices, in one or more chassis. For more information about TClk synchronization, refer to the NI-TClk Synchronization Help, which is located within the NI High-Speed Digitizers Help. For other configurations, including multichassis systems, contact NI Technical Support at ni.com/support.

#### **PXIe-5622 TClk Specifications**

- Specifications measured in an NI PXIe-1062Q chassis.

- All parameters set to identical values for each PXIe-5622.

- Sample Clock set to 150 MS/s and all filters are disabled.

Note Although you can use NI-TClk to synchronize non-identical devices, these specifications apply only to synchronizing identical devices.

| Intermodule synchronization using NI-TClk for identical devices                          |                     |  |

|------------------------------------------------------------------------------------------|---------------------|--|

| Skew (caused by clock and analog path delay differences; no manual adjustment performed) | ≤500 ps,<br>typical |  |

| Average skew after manual adjustment <sup>[12]</sup>                                     | ≤4 ps, typical      |  |

| Sample Clock delay/adjustment resolution | ≤4 ps, typical |

|------------------------------------------|----------------|

|------------------------------------------|----------------|

# **Waveform Specifications**

| Onboard memory sizes <sup>[13]</sup>                                                                                                          |                           |                             |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-----------------------------|--|

| 64 MB per channel option                                                                                                                      |                           | 32 megasamples per channel  |  |

| 256 MB per                                                                                                                                    | channel option            | 128 megasamples per channel |  |

| Allocated o                                                                                                                                   | onboard memory per record |                             |  |

| Real data $($ Record Length $\times$ 2 bytes/S $)$ + 480 bytes, rounded up to the next multiple of 128 bytes $)$ (minimum 512 bytes) $)$ [14] |                           |                             |  |

| Complex data                                                                                                                                  |                           |                             |  |

| Minimum record length 1 sample                                                                                                                |                           | 1 sample                    |  |

| Number of pretrigger samples, single-record mode and multiple-record mode  Zero up to full record length                                      |                           | -                           |  |

| Number of posttrigger samples, single-record mode and multiple-<br>record mode  Zero up to full record length                                 |                           | -                           |  |

| Maximum number of records in onboard memory <sup>[15]</sup> 100,000                                                                           |                           |                             |  |

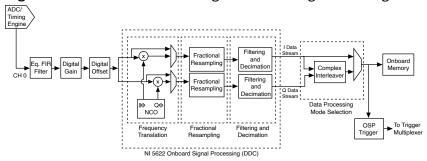

## **Onboard Signal Processing (OSP)**

Figure 9. PXIe-5622 Onboard Signal Processing Block Diagram

Note To use onboard signal processing (OSP) on the PXIe-5622, set the DDC Enabled property/attribute to TRUE.

The following OSP operations are available:

- Send one IF signal to CH 0 and perform quadrature downconversion on the signal (complex data is returned).

- Send a signal to CH 0 and perform alias-protected decimation (real data is returned).

- Send a signal to CH 0 and perform real downconversion on the signal (real data is returned).

| Number of digital downconverters (DDCs)                                                                          | One                              |

|------------------------------------------------------------------------------------------------------------------|----------------------------------|

| Data processing modes                                                                                            | Real (I path only); Complex (IQ) |

| OSP decimation (protects acquired data from high-frequency aliasing within the ADC Nyquist zone) <sup>[16]</sup> |                                  |

| Range                                                                                                            | 1, 2, 4, 6, 8, 10                |

| Multiples of 4 range                                                                                             | 12 to 4,096                      |

| Multiples of 8 range                                        |              | 4,096 to 8,192                                                         |  |

|-------------------------------------------------------------|--------------|------------------------------------------------------------------------|--|

| Multiples of 16 range                                       |              | 8,192 to 16,384                                                        |  |

| Fractional resampling enabled                               |              | 2 to 16,384 to 48 bits of precision                                    |  |

| Sample rate range, OSP enabled                              | [17]         |                                                                        |  |

| Internal sample clock timebase                              |              | 75 MS/s with fractional resampling; or to 150 MS,<br>tional resampling |  |

| External sample clock OSP decimation factor <sup>[18]</sup> | Sample clock | k timebase/OSP decimation                                              |  |

| Bandwidth <sup>[19]</sup>                                   |              |                                                                        |  |

| Real flat bandwidth                                         |              | 0.4 × Sample Rate                                                      |  |

| Complex flat bandwidth                                      |              | 0.8 × Sample Rate                                                      |  |

# **Complex Flat Bandwidth Example**

Complex bandwidth is 60 MHz with a complex sample rate of 75 MS/s.

Using a decimation rate of 1 (sample rate of 150 MS/s with internal clock) bypasses the filters in the OSP block.

# **OSP Digital Gain and Offset**

| Digital gain and offset resolution         | 18 bits                                            |

|--------------------------------------------|----------------------------------------------------|

| Digital gain range                         | ±1.5 ×   <b>ADC Data</b>   [20]                    |

| Digital offset, applied after digital gain | (-0.4 × Vertical Range) to (+0.4 × Vertical Range) |

| Output <sup>[21]</sup>                     | (ADC Data × Digital Gain) + Digital Offset         |

# **OSP Numerically-Controlled Oscillator (NCO)**

| Frequency range <sup>[22]</sup>  |                 |                                          |

|----------------------------------|-----------------|------------------------------------------|

| Internal sample clock timebase   | 0 MHz to 75 MHz |                                          |

| External sample clock timebase   | 0 Hz            | to (0.5 × <b>Sample Clock Timebase</b> ) |

| Frequency resolution             |                 |                                          |

| Internal sample clock timebase   |                 | 533 nHz                                  |

| External sample clock timebase   |                 | Sample Clock Timebase / 2 <sup>48</sup>  |

| I and Q phase resolution 0.0055° |                 | 0.0055°                                  |

# **OSP Digital Performance**

| Maximum NCO spur                                                                                    | <-100<br>dBFS |

|-----------------------------------------------------------------------------------------------------|---------------|

| Decimating filter passband ripple, passband is from 0 to (0.4 × <i>IQ Rate</i> )                    | < 0.1 dB      |

| Decimating filter Out-of-Band suppression, stopband suppression from (0.6 $\times$ <i>IQ Rate</i> ) | > 80 dB       |

# OSP IF Demodulation Typical Performance: Modulation Error Ratio (MER)

|                                                          |                                                                                             |                                                                                                                 | Direct path carrier frequency: 20 MHz (signal source: NI PXI-5441)                 |                                                                                                                 |

|----------------------------------------------------------|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

|                                                          | Internal Reference<br>Clocks (source and<br>receiver unlocked to<br>any external reference) | PXI chassis Reference Clocks (source and receiver locked to PXIe 100 MHz or PXI 10 MHz chassis backplane clock) | Internal Reference Clocks (source and receiver unlocked to any external reference) | PXI chassis Reference Clocks (source and receiver locked to PXIe 100 MHz or PXI 10 MHz chassis backplane clock) |

| GSM physical layer, typical. [23]                        | 50 dB                                                                                       | 59 dB                                                                                                           | 48 dB                                                                              | 62 dB <sup>[24]</sup>                                                                                           |

| W-CDMA<br>physical<br>layer,<br>typical. <sup>[25]</sup> | 47 dB                                                                                       | 50 dB                                                                                                           | 39 dB                                                                              | 58 dB                                                                                                           |

| DVB<br>physical<br>layer,                                | 46 dB                                                                                       | 48 dB                                                                                                           | 40 dB                                                                              | 56 dB                                                                                                           |

|                                                      |                                                                                             |                                                                                                                 | Direct path carrier frequency: 20 MHz (signal source: NI PXI-5441)                 |                                                                                                                 |

|------------------------------------------------------|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

|                                                      | Internal Reference<br>Clocks (source and<br>receiver unlocked to<br>any external reference) | PXI chassis Reference Clocks (source and receiver locked to PXIe 100 MHz or PXI 10 MHz chassis backplane clock) | Internal Reference Clocks (source and receiver unlocked to any external reference) | PXI chassis Reference Clocks (source and receiver locked to PXIe 100 MHz or PXI 10 MHz chassis backplane clock) |

| typical. <sup>[26]</sup>                             |                                                                                             |                                                                                                                 |                                                                                    |                                                                                                                 |

| 20<br>MSymbols/s<br>QAM,<br>typical. <sup>[27]</sup> | 43 dB                                                                                       | 44 dB                                                                                                           | 37 dB                                                                              | 49 dB                                                                                                           |

| 26<br>MSymbols/s<br>QAM,<br>typical. <sup>[28]</sup> | 39 dB                                                                                       | 37 dB                                                                                                           | 36 dB                                                                              | 40 dB                                                                                                           |

| 34<br>MSymbols/s<br>QAM,<br>typical. <sup>[29]</sup> | 38 dB                                                                                       | 37 dB                                                                                                           | 38 dB                                                                              | 37 dB                                                                                                           |

## Calibration

| Self-calibration              | Calibrates absolute amplitude accuracy.                                        |

|-------------------------------|--------------------------------------------------------------------------------|

| External calibration          | Calibrates absolute and relative (flatness) amplitude accuracy, VCXO accuracy. |

| External calibration interval | 1 year                                                                         |

| Warm-up time | 15 minutes |

|--------------|------------|

|              |            |

#### **Software**

#### **Driver Software**

Driver support for this device was first available in NI-SCOPE 3.5.

NI-SCOPE is an IVI-compliant driver that allows you to configure, control, and calibrate the PXIe-5622. NI-SCOPE provides application programming interfaces for many development environments.

#### **Application Software**

NI-SCOPE provides programming interfaces, documentation, and examples for the following application development environments:

- LabVIEW

- LabWindows<sup>™</sup>/CVI<sup>™</sup>

- Measurement Studio

- Microsoft Visual C/C++

- .NET (C# and VB.NET)

#### **Interactive Soft Front Panel and Configuration**

The NI-SCOPE Soft Front Panel (SFP) allows interactive control of the PXIe-5622.

Interactive control of the PXIe-5622 was first available in NI-SCOPE SFP version 3.5. The NI-SCOPE SFP is included on the NI-SCOPE media.

NI Measurement Automation Explorer (MAX) also provides interactive configuration and test tools for the PXIe-5622. MAX is included on the NI-SCOPE media.

#### **Power**

| Maximum power consumption, at highest operating temperature |        |  |

|-------------------------------------------------------------|--------|--|

| +3.3 VDC                                                    | 1.75 A |  |

| +12 VDC                                                     | 2.25 A |  |

| Total power                                                 | 32.8 W |  |

# **Physical Characteristics**

| Dimensions | 21.6 cm × 2.0 cm × 13.0 cm (8.5 in. × 0.8 in. × 5.1 in.)  3U, one slot, PXI/cPCI Module, PXI Express compatible |

|------------|-----------------------------------------------------------------------------------------------------------------|

| Weight     | 400 g (14.1 oz)                                                                                                 |

## **Environment**

| Maximum altitude | 2,000 m (800 mbar) (at 25 °C ambient temperature) |

|------------------|---------------------------------------------------|

| Pollution Degree | 2                                                 |

Indoor use only.

# **Operating Environment**

| Ambient<br>temperature<br>range | 0 °C to 55 °C (Tested in accordance with IEC 60068-2-1 and IEC 60068-2-2. Meets MIL-PRF-28800F Class 3 low temperature limit and MIL-PRF-28800F Class 2 high temperature limit.) |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Relative<br>humidity<br>range   | 10% to 90%, noncondensing (Tested in accordance with IEC 60068-2-56.)                                                                                                            |

# **Storage Environment**

| Ambient temperature range | -40 °C to 71 °C (Tested in accordance with IEC 60068-2-1 and IEC 60068-2-2. Meets MIL-PRF-28800F Class 3 limits.) |

|---------------------------|-------------------------------------------------------------------------------------------------------------------|

| Relative humidity range   | 5% to 95%, noncondensing (Tested in accordance with IEC 60068-2-56.)                                              |

## **Shock and Vibration**

| Operating shock  | 30 g peak, half-sine, 11 ms pulse (Tested in accordance with IEC 60068-2-27. Meets MIL-PRF-28800F Class 2 limits.)                                 |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Random vibration |                                                                                                                                                    |  |

| Operating        | 5 Hz to 500 Hz, 0.3 g <sub>rms</sub> (Tested in accordance with IEC 60068-2-64.)                                                                   |  |

| Nonoperating     | 5 Hz to 500 Hz, 2.4 g <sub>rms</sub> (Tested in accordance with IEC 60068-2-64. Test profile exceeds the requirements of MIL-PRF-28800F, Class 3.) |  |

## **Compliance and Certifications**

### **Safety**

This product is designed to meet the requirements of the following electrical equipment safety standards for measurement, control, and laboratory use:

- IEC 61010-1, EN 61010-1

- UL 61010-1, CSA C22.2 No. 61010-1

Note For UL and other safety certifications, refer to the product label or the Online Product Certification section.

#### **Electromagnetic Compatibility**

This product meets the requirements of the following EMC standards for electrical equipment for measurement, control, and laboratory use:

- EN 61326-1 (IEC 61326-1): Class A emissions; Basic immunity

- EN 55011 (CISPR 11): Group 1, Class A emissions

- EN 55022 (CISPR 22): Class A emissions

- EN 55024 (CISPR 24): Immunity

- AS/NZS CISPR 11: Group 1, Class A emissions

- AS/NZS CISPR 22: Class A emissions

- FCC 47 CFR Part 15B: Class A emissions

- ICES-001: Class A emissions

**Note** In the United States (per FCC 47 CFR), Class A equipment is intended for use in commercial, light-industrial, and heavy-industrial locations. In Europe, Canada, Australia, and New Zealand (per CISPR 11), Class A equipment is intended for use only in heavy-industrial locations.

**Note** Group 1 equipment (per CISPR 11) is any industrial, scientific, or medical equipment that does not intentionally generate radio frequency energy for the treatment of material or inspection/analysis purposes.

**Note** For EMC declarations, certifications, and additional information, refer to the <u>Online Product Certification</u> section.

## CE Compliance ( E

This product meets the essential requirements of applicable European Directives, as follows:

- 2014/35/EU; Low-Voltage Directive (safety)

- 2014/30/EU; Electromagnetic Compatibility Directive (EMC)

#### **Online Product Certification**

Refer to the product Declaration of Conformity (DoC) for additional regulatory compliance information. To obtain product certifications and the DoC for this product, visit <u>ni.com/certification</u>, search by model number or product line, and click the appropriate link in the Certification column.

#### **Environmental Management**

NI is committed to designing and manufacturing products in an environmentally responsible manner. NI recognizes that eliminating certain hazardous substances from our products is beneficial to the environment and to NI customers.

For additional environmental information, refer to the *Minimize Our Environmental Impact* web page at <u>ni.com/environment</u>. This page contains the environmental regulations and directives with which NI complies, as well as other environmental information not included in this document.

Waste Electrical and Electronic Equipment (WEEE)

**EU Customers** At the end of the product life cycle, all NI products must be disposed of according to local laws and regulations. For more information about how to recycle NI products in your region, visit <u>ni.com/environment/weee</u>.

#### 电子信息产品污染控制管理办法(中国RoHS)

中国客户 National Instruments符合中国电子信息产品中限制使用某些有 害物质指令(RoHS)。关于National Instruments中国RoHS合规性信息,请登 录 ni.com/environment/rohs china。(For information about China RoHS compliance, go to ni.com/environment/rohs china.)