# PCle-5785 Specifications

# **Contents**

| DC10_5785 Si | nacifications |      |      | : |

|--------------|---------------|------|------|---|

| CIE-2102 3   | pecificacions | <br> | <br> |   |

# PCIe-5785 Specifications

#### **Definitions**

**Warranted** specifications describe the performance of a model under stated operating conditions and are covered by the model warranty.

**Characteristics** describe values that are relevant to the use of the model under stated operating conditions but are not covered by the model warranty.

- *Typical* specifications describe the performance met by a majority of models.

- **Nominal** specifications describe an attribute that is based on design, conformance testing, or supplemental testing.

- *Measured* specifications describe the measured performance of a representative model.

Specifications are *Typical* unless otherwise noted.

#### Digital I/O

| Connector   | Molex™ Nano-Pitch I/O™      |

|-------------|-----------------------------|

| 5.0 V Power | ±5%, 50 mA maximum, nominal |

**Table 1.** Digital I/O Signal Characteristics

| Signal                      | Туре                  | Direction     |

|-----------------------------|-----------------------|---------------|

| MGT Tx± <03> $[1]$          | Xilinx UltraScale GTH | Output        |

| MGT Rx± <03> <sup>[1]</sup> | Xilinx UltraScale GTH | Input         |

| DIO <07>                    | Single-ended          | Bidirectional |

| Signal | Туре   | Direction    |

|--------|--------|--------------|

| 5.0 V  | DC     | Output       |

| GND    | Ground | <del>-</del> |

# Digital I/O Single-Ended Channels

| Number of channels                        | 8                                 |

|-------------------------------------------|-----------------------------------|

| Signal type                               | Single-ended                      |

| Voltage families                          | 3.3 V, 2.5 V, 1.8 V, 1.5 V, 1.2 V |

| Input impedance                           | 100 kΩ, nominal                   |

| Output impedance                          | 50 Ω, nominal                     |

| Direction control                         | Per channel                       |

| Minimum required direction change latency | 200 ns                            |

| Maximum output toggle rate                | 60 MHz with 100 μA load, nominal  |

**Table 2.** Digital I/O Single-Ended DC Signal Characteristics $^{[2]}$

| Voltage<br>Family (V) | V <sub>IL</sub><br>(V) | V <sub>IH</sub> (V) | V <sub>OL</sub> (100 μA Load)<br>(V) | V <sub>OH</sub> (100 μA Load)<br>(V) | Maximum DC Drive<br>Strength (mA) |

|-----------------------|------------------------|---------------------|--------------------------------------|--------------------------------------|-----------------------------------|

| 3.3                   | 0.8                    | 2.0                 | 0.2                                  | 3.0                                  | 24                                |

| 2.5                   | 0.7                    | 1.6                 | 0.2                                  | 2.2                                  | 18                                |

| Voltage<br>Family (V) | V <sub>IL</sub><br>(V) | V <sub>IH</sub> (V) | V <sub>OL</sub> (100 μA Load)<br>(V) | V <sub>OH</sub> (100 μA Load)<br>(V) | Maximum DC Drive<br>Strength (mA) |

|-----------------------|------------------------|---------------------|--------------------------------------|--------------------------------------|-----------------------------------|

| 1.8                   | 0.62                   | 1.29                | 0.2                                  | 1.5                                  | 16                                |

| 1.5                   | 0.51                   | 1.07                | 0.2                                  | 1.2                                  | 12                                |

| 1.2                   | 0.42                   | 0.87                | 0.2                                  | 0.9                                  | 6                                 |

# Digital I/O High-Speed Serial MGT<sup>[3]</sup>

**Note** MGTs are available on devices with KU040 and KU060 FPGAs only.

| Data rate                 | 500 Mbps to 16.375 Gbps, nominal |

|---------------------------|----------------------------------|

| Number of Tx channels     | 4                                |

| Number of Rx channels     | 4                                |

| I/O AC coupling capacitor | 100 nF                           |

#### MGT TX± Channels<sup>[4]</sup>

| Minimum differential output voltage <sup>[5]</sup> | 170 mV pk-pk into 100 $\Omega$ , nominal |

|----------------------------------------------------|------------------------------------------|

| I/O coupling                                       | AC-coupled, includes 100 nF capacitor    |

#### MGT RX± Channels

| Differential input voltage range |  |

|----------------------------------|--|

|----------------------------------|--|

| ≤ 6.6 Gb/s                    | 150 mV pk-pk to 2000 mV pk-pk, nominal |                                         |  |

|-------------------------------|----------------------------------------|-----------------------------------------|--|

| > 6.6 Gb/s                    | 150 mV pk-pk to 1250 mV pk-pk, nominal |                                         |  |

| Differential input resistance |                                        | 100 $\Omega$ , nominal                  |  |

| I/O coupling                  |                                        | DC-coupled, requires external capacitor |  |

#### **Reconfigurable FPGA**

PCIe-5785 modules are available with multiple FPGA options. The following table lists the FPGA specifications for the PCIe-5785 FPGA options.

Table 3. Reconfigurable FPGA Options

|                                      | KU035                                                                                               | KU040   | KU060   |

|--------------------------------------|-----------------------------------------------------------------------------------------------------|---------|---------|

| LUTs                                 | 203,128                                                                                             | 242,200 | 331,680 |

| DSP48 slices<br>(25 × 18 multiplier) | 1,700                                                                                               | 1,920   | 2,760   |

| Embedded Block RAM                   | 19.0 Mb                                                                                             | 21.1 Mb | 38.0 Mb |

| Data Clock Domain                    | 200 MHz, 16 samples per cycle per channel (dual chann<br>32 samples per cycle (single channel mode) |         | • •     |

| Timebase reference sources           | Onboard 100 MHz oscillator                                                                          |         |         |

| Data transfers                       | DMA, interrupts, DMA, interrupts, programmed I/O, programmed I/O multi-gigabit transceivers         |         |         |

| Number of DMA channels               |                                                                                                     | 60      |         |

**Note** The Reconfigurable FPGA Options table depicts the total number of

FPGA resources available on the part. The number of resources available to the user is slightly lower, as some FPGA resources are consumed by boardinterfacing IP for PCI Express, device configuration, and various board I/O. For more information, contact NI support.

#### **Onboard DRAM**

| Memory size                   | 4 GB (2 banks of 2 GB)      |

|-------------------------------|-----------------------------|

| DRAM clock rate               | 1064 MHz                    |

| Physical bus width            | 32 bit                      |

| LabVIEW FPGA DRAM clock rate  | 267 MHz                     |

| LabVIEW FPGA DRAM bus width   | 256 bit per bank            |

| Maximum theoretical data rate | 17 GB/s (8.5 GB/s per bank) |

#### **Analog Input**

#### **General Characteristics**

| Number of channels | 2, single-ended, simultaneously sampled |

|--------------------|-----------------------------------------|

| Connector type     | SMA                                     |

| Input impedance                   | 50 Ω                           | 50 Ω                 |                         |  |

|-----------------------------------|--------------------------------|----------------------|-------------------------|--|

| Input coupling                    | AC                             | AC                   |                         |  |

| Sample Clock                      |                                |                      |                         |  |

| Internal Sample Clock 3.2 GHz     |                                |                      | 3.2 GHz                 |  |

| External Sample Clock             | 2.8 GHz to 3.2 GHz             |                      |                         |  |

| Sample Rate                       |                                |                      |                         |  |

| Dual channel mode                 |                                | 3.2 GS/s per channel |                         |  |

| Single channel mode               |                                | 6.4 GS/s             |                         |  |

| Analog-to-digital converter (ADC) | ADC12DJ3200, 12-bit resolution |                      | 3200, 12-bit resolution |  |

| Input latency <sup>[6]</sup>      | 239 ns                         |                      |                         |  |

# **Typical Specifications**

| Full-scale input range | 1.25 V pk-pk (5.92 dBm) at 10 MHz |

|------------------------|-----------------------------------|

| AC gain accuracy       | ±0.11 dB at 10 MHz                |

| DC offset              | ±2.19 mV                          |

| Bandwidth (-3 dB) <sup>[7]</sup> 500 kHz to 6 GHz |  |

|---------------------------------------------------|--|

|---------------------------------------------------|--|

**Table 4.** Single-Tone Spectral Performance, Dual Channel Mode

|                                | Input Frequency |         |         |           |           |

|--------------------------------|-----------------|---------|---------|-----------|-----------|

|                                | 99.9 MHz        | 399 MHz | 999 MHz | 1.999 GHz | 2.499 GHz |

| SNR <sup>[8]</sup> (dBFS)      | 56.0            | 55.6    | 54.7    | 52.9      | 51.6      |

| SINAD <sup>[8]</sup><br>(dBFS) | 55.5            | 55.0    | 54.0    | 51.8      | 50.8      |

| SFDR (dBc)                     | -64.9           | -63.4   | -62.7   | -59.9     | -58.6     |

| ENOB <sup>[9]</sup> (bits)     | 8.9             | 8.8     | 8.7     | 8.3       | 8.1       |

**Table 5.** Single-Tone Spectral Performance, Single Channel  $\mathsf{Mode}^{[10]}$

| Input Frequency                |          |       |       |       |       |  |

|--------------------------------|----------|-------|-------|-------|-------|--|

| -                              | 99.9 MHz |       |       |       |       |  |

| SNR <sup>[8]</sup> (dBFS)      | 54.6     | 54.2  | 52.4  | 49.7  | 48.9  |  |

| SINAD <sup>[8]</sup><br>(dBFS) | 54.4     | 53.9  | 52.1  | 49.4  | 48.6  |  |

| SFDR (dBc)                     | -61.7    | -60.4 | -56.1 | -51.7 | -51.1 |  |

| ENOB <sup>[9]</sup> (bits)     | 8.7      | 8.7   | 8.4   | 7.9   | 7.8   |  |

**Table 6.** Noise Spectral Density $^{[11]}$

| Mode           | $\frac{nV}{\sqrt{Hz}}$ | dBm<br>Hz | dBFS<br>Hz |

|----------------|------------------------|-----------|------------|

| Dual channel   | 14.4                   | -143.8    | -149.2     |

| Single channel | 9.8                    | -147.2    | -152.6     |

**Note** Noise spectral density is verified using a 50  $\Omega$  terminator connected to

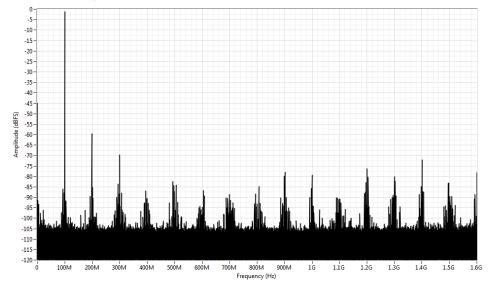

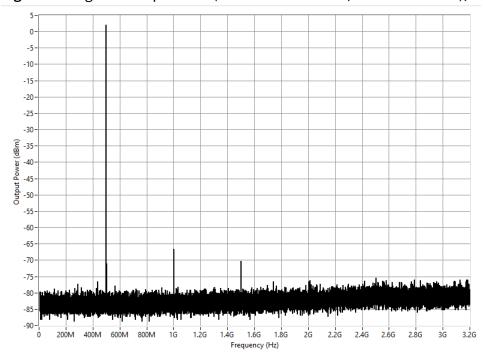

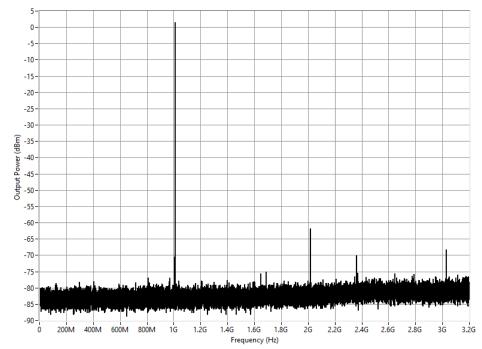

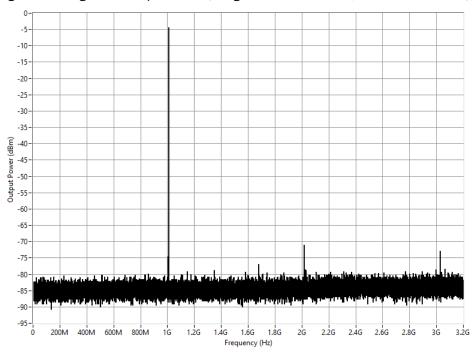

Figure 1. Single Tone Spectrum (Dual Channel Mode, 99.9 MHz, -1 dBFS, 3.2 kHz RBW), Measured

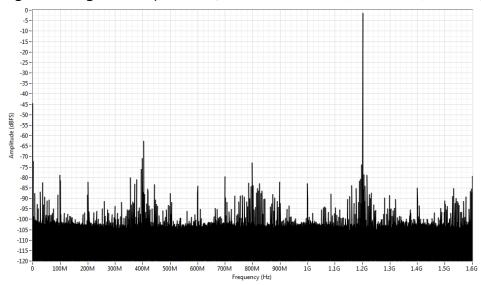

Figure 2. Single Tone Spectrum (Dual Channel Mode, 1.999 GHz, -1 dBFS, 3.2 kHz RBW), Measured

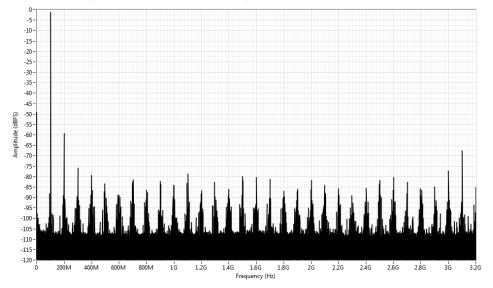

Figure 3. Single Tone Spectrum (Single Channel Mode, 99.9 MHz, -1 dBFS, 3.2 kHz RBW), Measured

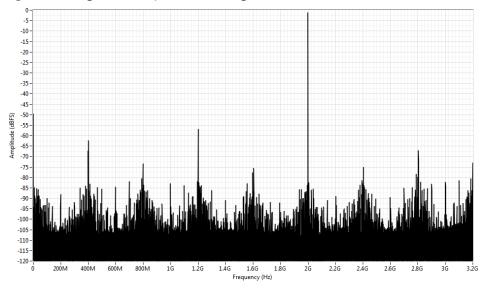

Figure 4. Single Tone Spectrum (Single Channel Mode, 1.999 GHz, -1 dBFS, 3.2 kHz RBW), Measured

| Channel-to-channel crosstalk, measured |          |  |

|----------------------------------------|----------|--|

| 99.9 MHz                               | -92.5 dB |  |

| 399 MHz                                | -85.5 dB |  |

| 999 MHz                                | -76.5 dB |  |

| 1.999 GHz | -68.8 dB |

|-----------|----------|

| 2.499 GHz | -67.4 dB |

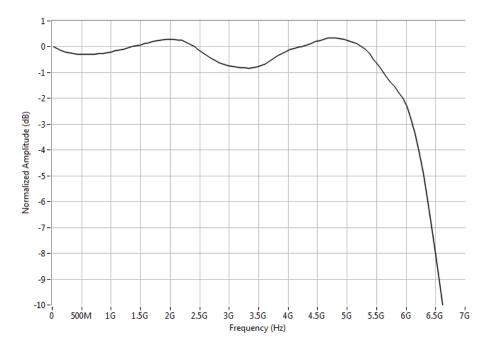

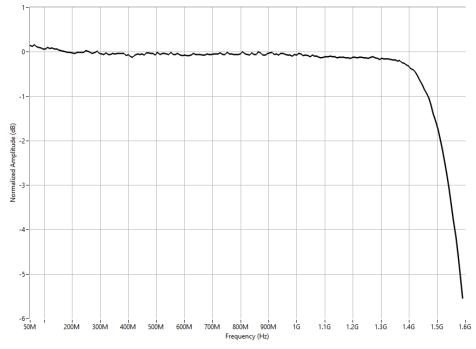

Figure 5. Analog Input Frequency Response, Measured

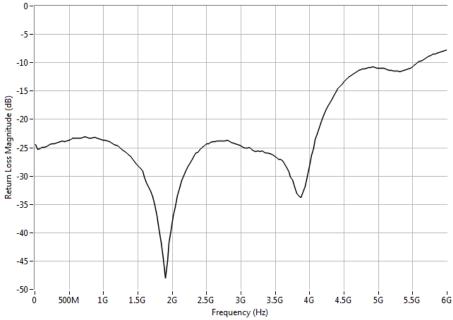

Figure 6. Input Return Loss, Measured

# **Analog Output**

#### **General Characteristics**

| Number of channels                      | 2, single-ended, simultaneously updated |          |  |

|-----------------------------------------|-----------------------------------------|----------|--|

| Connector type                          | SMA                                     |          |  |

| Output impedance                        | 50 Ω                                    |          |  |

| Output coupling AC                      |                                         |          |  |

| Update rate                             |                                         |          |  |

| Internal Sample Clock, 2x interpolation |                                         | 6.4 GS/s |  |

| External Sample Clock, 2x interpolation                |  |               |  | 6.4 GS/s <sup>[12]</sup> |

|--------------------------------------------------------|--|---------------|--|--------------------------|

| Data rate (per channel)                                |  |               |  |                          |

| Dual channel mode 3.2 GS/s, re                         |  | : GS/s, real  |  |                          |

| Single channel mode 3.2 GS/s, c                        |  | GS/s, complex |  |                          |

| Digital-to-analog converter (DAC)  DAC38RF82, 12-bit r |  | esolution     |  |                          |

| Output latency <sup>[13]</sup>                         |  |               |  |                          |

| DUC disabled                                           |  | 211 ns        |  |                          |

| DUC enabled                                            |  | 221 ns        |  |                          |

#### **Typical Specifications**

**Note** Due to a silicon flaw in the TI DAC38RF82 chip, there is a 0.5% chance of seeing a 50 mV glitch at the output of either channel after a bitfile redownload, invoking the Reset method explicitly or by closing the FPGA reference, or committing a new configuration.

| Full-scale output power <sup>[14]</sup>  |                     |  |

|------------------------------------------|---------------------|--|

| Dual Channel Mode                        | 2.85 dBm (878 mVpp) |  |

| Single Channel Mode -3.33 dBm (431 mVpp) |                     |  |

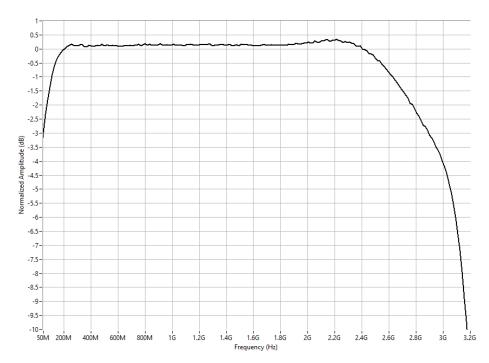

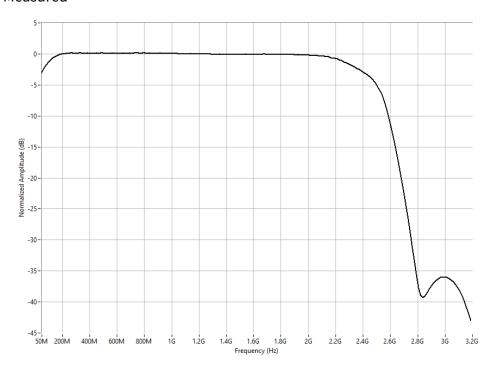

| Bandwidth (-3 dB) <sup>[15]</sup>        |                     |  |

| Dual Channel Mode                            | 3 MHz to 1.53 GHz  |

|----------------------------------------------|--------------------|

| Single Channel Mode (no anti-image filter)   | 60 MHz to 2.85 GHz |

| Single Channel Mode (with anti-image filter) | 60 MHz to 2.35 GHz |

**Table 7.** Single Tone Spectral Performance, Dual Channel  $\mathsf{Mode}^{[\underline{16}]}$

|              | Generation Frequency |       |

|--------------|----------------------|-------|

|              | 501 MHz 1.01 GHz     |       |

| 2nd HD (dBc) | -67.8                | -61.7 |

| 3rd HD (dBc) | -63.0                | -62.0 |

| SFDR (dBc)   | -63.0                | -61.7 |

**Table 8.** Single Tone Spectral Performance, Single Channel  $\mathsf{Mode}^{[\underline{16}]}$

|              | Generation Frequency |  |

|--------------|----------------------|--|

|              | 1.01 GHz             |  |

| 2nd HD (dBc) | -62.4                |  |

| 3rd HD (dBc) | -67.3                |  |

| SFDR (dBc)   | -62.4                |  |

**Table 9.** IMD3 Performance, Dual Channel Mode, Measured  $^{[17]}$

|            | Generation Frequency                        |       |

|------------|---------------------------------------------|-------|

|            | 501 MHz and 511 MHz 1.005 GHz and 1.015 GHz |       |

| IMD3 (dBc) | -73.9                                       | -67.6 |

**Table 10.** Noise Spectral Density  $^{[18]}$

|                | 501 MHz Generation Frequency |           |            |

|----------------|------------------------------|-----------|------------|

| Mode           | $\frac{nV}{\sqrt{Hz}}$       | dBm<br>Hz | dBFS<br>Hz |

| Dual Channel   | 1.18                         | -165.5    | -168.4     |

| Single Channel | 0.941                        | -167.5    | -164.2     |

**Figure 7.** Single Tone Spectrum (Dual Channel Mode, 501 MHz 0 dBFS), Measured [19]

**Figure 8.** Single Tone Spectrum (Dual Channel Mode, 1.01 GHz 0 dBFS), Measured  $^{[19]}$

**Figure 9.** Single Tone Spectrum (Single Channel Mode, 1.01 GHz 0 dBFS), Measured  $^{[19]}$

| Channel-to-channel crosstalk, measured [20] |         |

|---------------------------------------------|---------|

| 100 MHz                                     | -82 dBc |

| 500 MHz | -91 dBc |

|---------|---------|

| 1.0 GHz | -90 dBc |

| 1.5 GHz | -88 dBc |

| 2.0 GHz | -82 dBc |

| 2.5 GHz | -82 dBc |

$\textbf{Figure 10.} \ \textbf{Analog Output Dual Channel Mode Frequency Response, Measured} \\ ^{\underline{[21]}}$

Figure 11. Analog Output Single Channel Mode Frequency Response, No Anti-Image Filter,

# Measured<sup>[21]</sup>

Figure 12. Analog Output Single Channel Mode Frequency Response With Anti-Image Filter, Measured<sup>[22]</sup>

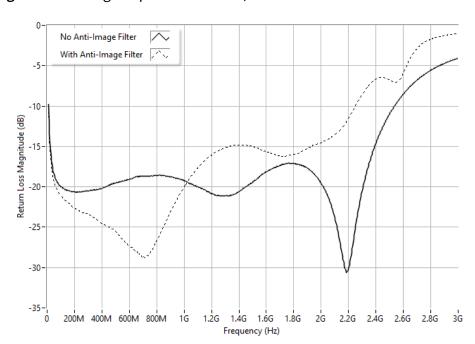

Figure 13. Analog Output Return Loss, Measured

# **REF/CLK IN**

#### **General Characteristics**

| Connector type           | SMA                                  |

|--------------------------|--------------------------------------|

| Input impedance          | 50 Ω                                 |

| Input coupling           | AC                                   |

| Input voltage range      | 0.35 V pk-pk to 3.5 V pk-pk, nominal |

| Absolute maximum voltage | ±12 V DC, 4 V pk-pk AC               |

| Duty cycle               | 45% to 55%                           |

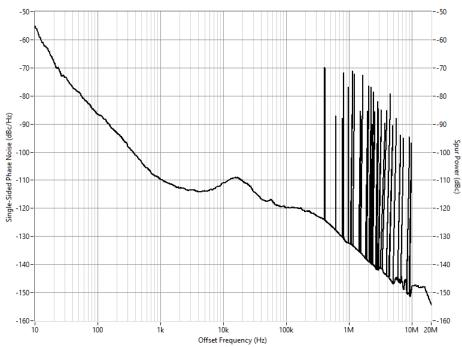

| Sample Clock jitter |                                                    |

|---------------------|----------------------------------------------------|

| Analog input        | 86.8 fs <sub>rms</sub> , measured <sup>[23]</sup>  |

| Analog output       | 198.8 fs <sub>rms</sub> , measured <sup>[24]</sup> |

**Table 11.** Clock Configuration Options

| Clock Configuration                                   | External Clock Frequency | Description                                                                                                                     |

|-------------------------------------------------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Internal Baseboard Reference<br>Clock <sup>[25]</sup> | 10 MHz                   | The internal Sample Clock locks<br>to the 10 MHz Reference Clock<br>provided from the FPGA<br>baseboard.                        |

| External Reference Clock (REF/<br>CLK IN)             | 10 MHz <sup>[26]</sup>   | The internal Sample Clock locks to an external Reference Clock, which is provided through the REF/CLK IN front panel connector. |

| External Sample Clock (REF/CLK IN)                    | 2.8 GHz to 3.2 GHz       | An external Sample Clock can<br>be provided through the REF/<br>CLK IN front panel connector.                                   |

-122.0 -124.0 -126.0 -128.0 -130.0 -132.0 꿀 -134.0 평 -136.0· -138.0 -140.0 -142.0 -144.0 -146.0 -148.0 -150.0 -152.0 -154.0 -156.0 -158.0 -160.0 -1.0k 100.0k Offset Frequency (Hz) 10.0k

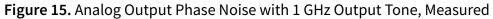

Figure 14. Analog Input Phase Noise with 800 MHz Input Tone, Measured

#### **Bus Interface**

| Card edge form factor PCI Express Gen-3 x8 | Card edge form factor | PCI Express Gen-3 x8 |

|--------------------------------------------|-----------------------|----------------------|

|--------------------------------------------|-----------------------|----------------------|

| x8 and x16 PCI Express slots | Slot compatibility |

|------------------------------|--------------------|

|------------------------------|--------------------|

# **Maximum Power Requirements**

**Note** Power requirements depend on the contents of the LabVIEW FPGA VI used in your application.

| +3.3 V              | 4.5 A |

|---------------------|-------|

| +12 V               | 5 A   |

| Maximum total power | 75 W  |

# **Physical**

| Dimensions (including I/O bracket, not including connectors) | 12.6 cm × 26.3 cm × 4 cm (5.0 in. × 10.4 in. × 1.6 in.) |

|--------------------------------------------------------------|---------------------------------------------------------|

| Weight                                                       | 990 g (35 oz)                                           |

| PCI Express mechanical form factor                           | Standard height, three-quarter length, double slot      |

| Integrated air mover (fan)                                   | Yes                                                     |

| Maximum rear panel exhaust airflow                           | 84 m <sup>3</sup> /h (50 CFM) (without any chassis      |

| impedance) |

|------------|

|            |

#### **Environmental**

| Maximum altitude | 2,000 m (800 mbar) (at 25 °C ambient temperature) |

|------------------|---------------------------------------------------|

| Pollution degree | 2                                                 |

Indoor use only.

# **Operating Environment**

| Operating temperature, local <sup>[27]</sup> | 0 °C to 45 °C                |

|----------------------------------------------|------------------------------|

| Operating humidity                           | 10% to 90% RH, noncondensing |

# **Storage Environment**

| Ambient temperature range | -20 °C to 70 °C             |

|---------------------------|-----------------------------|

| Relative humidity range   | 5% to 95% RH, noncondensing |