# PXIe-6571 Specifications

# **Contents**

| PXIe-6571 Specifications | 3 |

|--------------------------|---|

| TAIC 0011 Openications   | 9 |

# PXIe-6571 Specifications

These specifications apply to the PXIe-6571 (8-channel) and PXIe-6571 (32-channel).

Note Unless otherwise noted, "PXIe-6571" encompasses both the 8-channel and 32-channel variants.

When using the PXIe-6571 in the Semiconductor Test System, refer to the Semiconductor Test System Specifications.

#### **Definitions**

Warranted specifications describe the performance of a model under stated operating conditions and are covered by the model warranty. Warranted specifications account for measurement uncertainties, temperature drift, and aging. Warranted specifications are ensured by design or verified during production and calibration.

**Characteristics** describe values that are relevant to the use of the model under stated operating conditions but are not covered by the model warranty.

- *Typical* specifications describe the performance met by a majority of models.

- **Nominal** specifications describe an attribute that is based on design, conformance testing, or supplemental testing.

Specifications are *Nominal* unless otherwise noted.

#### **Conditions**

Specifications are valid under the following conditions unless otherwise noted.

- Operating temperature of 0 °C to 40 °C

- Chassis with slot cooling capacity as follows:

- PXIe-6571 (8-channel): ≥58 W

- PXIe-6571 (32-channel): 82 W

- Operating temperature within ±5 °C of the last self-calibration temperature

- Recommended calibration interval of 1 year. The PXIe-6571 will not meet specifications unless operated within the recommended calibration interval.

- DUT Ground Sense (DGS) same potential as the Ground (GND) pins

- 30-minute warmup time before operation

**Note** When the pin electronics on the PXIe-6571 are in the disconnect state, some I/O protection and sensing circuitry remain connected. Do not subject the PXIe-6571 to voltages beyond the supported measurement range.

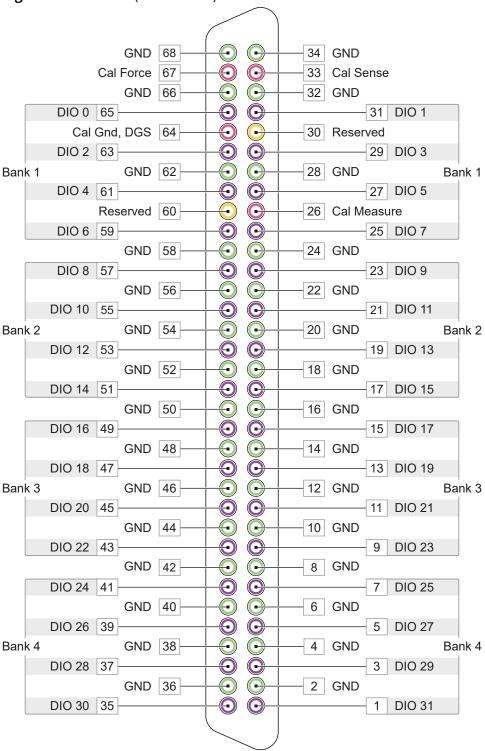

#### PXIe-6571 Pinout

The PXIe-6571 exposes signal terminals via a VHDCI connector.

1. For guidance on thermal management best practices, visit <u>ni.com/info</u> and enter the Info Code ThermalManagement.

**(** 34 GND GND 68 Cal Force 67 33 Cal Sense **(-)** GND 66 32 GND 0 31 DIO 1 DIO 0 65 Cal Gnd, DGS 64 **(** 30 Reserved 0 DIO 2 63 29 DIO 3 GND 62 28 GND Bank 1 Bank 1 0 27 DIO 5 DIO 4 61 -0 Reserved 60 26 Cal Measure **①** DIO 6 59 0 25 DIO 7 24 GND GND 58 23 Reserved Reserved 57 0 22 GND GND 56 Reserved 55 21 Reserved GND 54 20 GND Bank 2 Bank 2 Reserved 53 19 Reserved  $\bigcirc$ GND 52 0 18 GND Reserved 51 **(** 17 Reserved GND 50 16 GND Reserved 49 **(** 15 Reserved GND 48 14 GND Reserved 47 13 Reserved Bank 3 0 12 GND GND 46 Bank 3 Reserved 45 11 Reserved 10 GND GND 44 Reserved 43 9 Reserved ( ) 8 GND GND 42  $\odot$ Reserved 41 Reserved GND 40 6 GND Reserved 39 Reserved • 4 GND Bank 4 GND 38 Bank 4 Reserved 37 3 Reserved 2 GND  $\odot$ GND 36 Reserved Reserved 35 - 1 |

Figure 1. PXIe-6571 (8-channel) Connector Pinout

Figure 2. PXIe-6571 (32-channel) Connector Pinout

Table 1. PXIe-6571 Digital Data and Control Connector Pins/Signal Descriptions

| Signal<br>Type                                             | Signal<br>Name | Signal Description                                                                                    |  |

|------------------------------------------------------------|----------------|-------------------------------------------------------------------------------------------------------|--|

| Data                                                       | DIO<br><031>   | Bidirectional PPMU-capable digital I/O data channels 0 through 31.                                    |  |

| Cuavia                                                     | GND            | Instrument ground. Acts as the default ground reference when DUT Ground Sense (DGS) is not connected. |  |

| Ground                                                     | DGS            | Optional DGS for improved accuracy at higher currents in some configurations.                         |  |

| CAL MEASURE  CAL SENSE  Resource for external calibration. |                |                                                                                                       |  |

|                                                            |                | Resource for external calibration.                                                                    |  |

|                                                            | CAL GND        |                                                                                                       |  |

|                                                            | CAL<br>FORCE   |                                                                                                       |  |

| N/A                                                        | RESERVED       | These terminals are reserved for future use. Do not connect to these pins.                            |  |

Note The digital I/O data channels of 32-channel digital pattern instruments are split into banks for PPMU operation efficiency: DIO <0..7>, DIO <8..15>, DIO <16..23>, DIO <24..31>. PPMU measurements run in parallel when you take measurements on channels across different banks. Taking PPMU measurements simultaneously with channels on the same bank impacts test time performance based on certain measurement settings. Test time performance for frequency counter measurements is not impacted by taking multiple frequency counter measurements on channels in the same bank.

#### General

| Channel count         |   |

|-----------------------|---|

| PXIe-6571 (8-channel) | 8 |

| PXIe-6571 (32-channel)                                    | 32  |

|-----------------------------------------------------------|-----|

| System channel count, PXIe-6571 (32-channel) <sup>2</sup> | 512 |

| Multi-site resources per instrument |   |

|-------------------------------------|---|

| PXIe-6571 (8-channel)               | 8 |

| PXIe-6571 (32-channel)              | 8 |

| Large Vector Memory (LVM)                | 128M vectors                        |

|------------------------------------------|-------------------------------------|

| History RAM (HRAM)                       | (8,192 / <b>n</b> sites) - 1 cycles |

| Maximum allowable offset (DGS minus GND) | ±300 mV                             |

| Supported measurement range <sup>3</sup> | -2 V to 7 V <sup>4</sup>            |

- 2. The **system channel count** is the maximum number of channels available when using multiple PXIe-6571 (32-channel) instruments in a single chassis as a digital subsystem within an application system. Some functionality described in this document requires that a PXIe-6674T synchronization module be used in conjunction with each digital subsystem.

- 3. If the total voltage sourced or driven on any pin relative to GND exceeds the supported measurement range, instrument performance may be degraded.

- 4. **Voltage** > 6 V requires the Extended Voltage Range mode of operation. For additional information, refer to **PPMU Force Voltage**.

## **Vector Timing**

| Maximum vector rate      | 100 MHz                            |

|--------------------------|------------------------------------|

| Vector period range      | 10 ns to 40 μs (100 MHz to 25 kHz) |

| Vector period resolution | 38 fs                              |

| Timing control |                                          |  |

|----------------|------------------------------------------|--|

| Vector period  | Vector-by-vector on the fly              |  |

| Edge timing    | Per channel, vector-by-vector on the fly |  |

| Drive formats  | Per channel, vector-by-vector on the fly |  |

# Clocking

| Master clock source     | PXIe_CLK100 <sup>5</sup>                                                       |

|-------------------------|--------------------------------------------------------------------------------|

| Sequencer clock domains | One (independent sequencer clock domains on a single instrument not supported) |

## **Drive and Compare Formats**

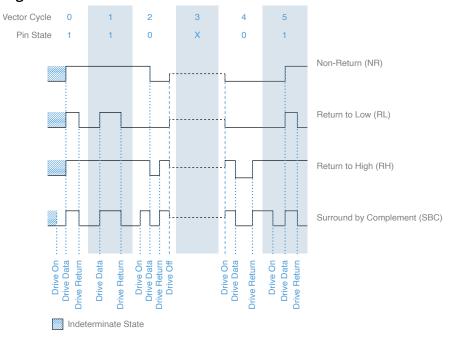

## Drive formats<sup>6[6]</sup>

- 5. Sourced from chassis 100 MHz backplane reference clock, external 10 MHz reference, or PXIe-6674T.

- 6. The maximum vector rate for patterns may be limited by the pulse width requirements, which may

| 100 MHz maximum vector rate | Non-Return (NR), Return to Low (RL), Return to High (RH) |

|-----------------------------|----------------------------------------------------------|

| 50 MHz maximum vector rate  | Surround by Complement (SBC) <sup>7</sup>                |

| Compare formats                 | Edge strobe |

|---------------------------------|-------------|

| Edge Multipliers <sup>[6]</sup> | 1x, 2x      |

not allow all formats and edge multipliers to be used up to the fastest vector rate.

7. The SBC format is not supported within the 2x edge multiplier mode.

Vector Cycle XX Pin State Non-Return (NR) Return to Low (RL) Return to High (RH) Indeterminate State

Figure 4. 2x Mode Drive Formats

#### **Pin Data States**

- 0—Drive zero

- 1—Drive one

- L—Compare low

- H—Compare high

- X—Do not drive; mask compare

- M—Compare midband, not high or low

- V—Compare high or low, not midband; store results from capture functionality if configured

- D—Drive data from source functionality if configured

- E—Expect data from source functionality if configured

- -- Repeat previous cycle; do not use a dash (-) for the pin state on the first vector of a pattern file unless the file is used only as a target of a jump or call operation

Note Termination mode settings affect the termination applied to all nondriving pin states. Non-drive states include L, H, M, V, X, E, and potentially -. Refer to the Programmable input termination mode specification for more information.

# **Edge Types**

| Drive edges                      | 6: drive on, drive data, drive return,<br>drive data 2, drive return 2, drive off |

|----------------------------------|-----------------------------------------------------------------------------------|

| Compare edge                     | 2: strobe, strobe 2                                                               |

| Number of time sets <sup>8</sup> | 31                                                                                |

# **Edge Generation Timing**

| Edge placement range |                                                 |

|----------------------|-------------------------------------------------|

| Minimum              | Start of vector period (0 ns)                   |

| Maximum              | 5 vector periods or 40 μs, whichever is smaller |

| Minimum required edge separation         |         |

|------------------------------------------|---------|

| Between any driven data change           | 3.75 ns |

| Between any Drive On and Drive Off edges | 5 ns    |

| Between Compare Strobes                  | 5 ns    |

8. 31 time sets can be configured. One additional time set, represented by a -, repeats the previous time set.

| Edge placement resolution | 39.0625 ps |

|---------------------------|------------|

|---------------------------|------------|

| Edge placement accuracy, drive <sup>9[9]</sup> |                                                                                           |

|------------------------------------------------|-------------------------------------------------------------------------------------------|

| Edge Multiplier = 1x, PXIe-6571 (32-channel)   | ±500 ps, warranted                                                                        |

| Edge Multiplier = 1x, PXIe-6571 (8-channel)    | ±500 ps, typical                                                                          |

| Edge Multiplier = 2x                           | <i>Bit Rate</i> ≤ 200 Mbps: ±500 ps, typical <i>Bit Rate</i> ≤ 266 Mbps: ±600 ps, typical |

| Edge placement accuracy, compare [9]         |                                                                                           |

|----------------------------------------------|-------------------------------------------------------------------------------------------|

| Edge Multiplier = 1x, PXIe-6571 (32-channel) | ±500 ps, warranted                                                                        |

| Edge Multiplier = 1x, PXIe-6571 (8-channel)  | ±500 ps, typical                                                                          |

| Edge Multiplier = 2x                         | <i>Bit Rate</i> ≤ 100 Mbps: ±500 ps, typical <i>Bit Rate</i> ≤ 133 Mbps: ±700 ps, typical |

| Overall timing accuracy <sup>[9]</sup>       |                    |

|----------------------------------------------|--------------------|

| Edge Multiplier = 1x, PXIe-6571 (32-channel) | ±1.5 ns, warranted |

9. For specifications in a Semiconductor Test System, refer to the *Semiconductor Test System* Specifications.

| Edge Multiplier = 1x, PXIe-6571 (8-channel) | ±1.5 ns, typical                                                             |

|---------------------------------------------|------------------------------------------------------------------------------|

| Edge Multiplier = 2x                        | Bit Rate ≤ 200 Mbps: ±1.5 ns, typical  Bit Rate ≤ 266 Mbps: ±1.8 ns, typical |

| 39.0625 ps | TDR deskew adjustment resolution |

|------------|----------------------------------|

|------------|----------------------------------|

# Driver

| Signal type         | Single-ended, referenced to the DGS pin when connected. Otherwise referenced to GND. |

|---------------------|--------------------------------------------------------------------------------------|

| Programmable levels | V <sub>IH</sub> , V <sub>IL</sub> , V <sub>TERM</sub>                                |

| Voltage levels                                                      |                                           |

|---------------------------------------------------------------------|-------------------------------------------|

| Range (V <sub>IH</sub> , V <sub>IL</sub> , V <sub>TERM</sub> )      | -2 V to 6 V                               |

| Minimum swing (V <sub>IH</sub> minus V <sub>IL</sub> )              | 400 mV, into a 1 M $\Omega$ load          |

| Resolution (V <sub>IH</sub> , V <sub>IL</sub> , V <sub>TERM</sub> ) | 122 μV                                    |

| Accuracy (V <sub>IH</sub> , V <sub>IL</sub> , V <sub>TERM</sub> )   | $\pm 15$ mV, 1 M $\Omega$ load, warranted |

| Maximum DC drive current   | ±32 mA            |

|----------------------------|-------------------|

| Output impedance           | 50 Ω              |

| Rise/fall time, 20% to 80% | 1.2 ns, up to 5 V |

# Comparator

| Signal type         | Single-ended, referenced to the DGS pin when connected. Otherwise referenced to GND. |

|---------------------|--------------------------------------------------------------------------------------|

| Programmable levels | V <sub>OH</sub> , V <sub>OL</sub>                                                    |

| Voltage levels                                  |                                         |  |

|-------------------------------------------------|-----------------------------------------|--|

| Range (V <sub>OH</sub> , V <sub>OL</sub> )      | -2 V to 6 V                             |  |

| Resolution (V <sub>OH</sub> , V <sub>OL</sub> ) | 122 μV                                  |  |

| Accuracy (V <sub>OH</sub> , V <sub>OL</sub> )   | ±25 mV, from -1.5 V to 5.8 V, warranted |  |

| Programmable input termination modes | High Z, 50 $\Omega$ to V <sub>TERM</sub> , Active Load |

|--------------------------------------|--------------------------------------------------------|

| Leakage current                      | <15 nA, in the High Z termination mode                 |

# **Active Load**

| Programmable levels | I <sub>OH</sub> , I <sub>OL</sub> |

|---------------------|-----------------------------------|

|---------------------|-----------------------------------|

| Commutating voltage (V <sub>COM</sub> ) |             |

|-----------------------------------------|-------------|

| Range                                   | -2 V to 6 V |

| Resolution                              | 122 μV      |

| Current levels |                                     |

|----------------|-------------------------------------|

| Range          | 1.5 mA to 16 mA                     |

| Resolution     | 488 nA                              |

| Accuracy       | 1 mA, 3 V over/under drive, typical |

# **PPMU Force Voltage**

| Signal<br>type | Single-ended, referenced to the DGS pin when connected. Otherwise referenced to GND. |

|----------------|--------------------------------------------------------------------------------------|

|----------------|--------------------------------------------------------------------------------------|

| Voltage levels |             |  |

|----------------|-------------|--|

| Range          | -2 V to 6 V |  |

|            | 6 V to 7 V in Extended Voltage Range <sup>10[10]</sup>                                                                                    |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Resolution | 122 μV                                                                                                                                    |

| Accuracy   | $\pm 15$ mV, 1 M $\Omega$ load, from -2 V to 6 V, warranted $\pm 50$ mV, 1 M $\Omega$ load, from 6 V to 7 V, typical $^{\left[10\right]}$ |

# **PPMU Measure Voltage**

| Signal<br>type | Single-ended, referenced to the DGS pin when connected. Otherwise referenced to GND. |

|----------------|--------------------------------------------------------------------------------------|

|----------------|--------------------------------------------------------------------------------------|

| Voltage levels |                  |

|----------------|------------------|

| Range          | -2 V to 6 V      |

| Resolution     | 228 μV           |

| Accuracy       | ±5 mV, warranted |

<sup>10.</sup> The Extended Voltage Range is an unwarranted mode of operation that allows the PMU to force voltages between 6 V and 7 V for applications that can tolerate more error than the normal force voltage accuracy.

#### **PPMU Force Current**

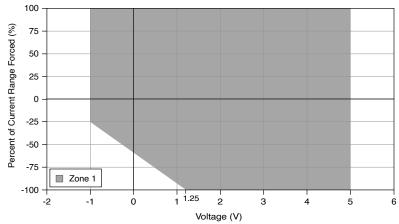

Table 2. PPMU Force Current Accuracy

| Range   | Resolution | Accuracy                                                  |

|---------|------------|-----------------------------------------------------------|

| ±2 μA   | 60 pA      |                                                           |

| ±32 μA  | 980 pA     |                                                           |

| ±128 μA | 3.9 nA     | ±1% of range for Zone 1 of<br><u>Figure 5</u> , warranted |

| ±2 mA   | 60 nA      | <u>rigare o,</u> warrantea                                |

| ±32 mA  | 980 nA     |                                                           |

Figure 5. Warranted Current Accuracy Zone for PPMU Force Current

**Note** The boundaries of Zone 1 are inclusive of that zone. The area outside of Zone 1 does not have a warranted specification for PPMU force current accuracy.

# How to Calculate PPMU Force Current Accuracy

- 1. Specify the desired forced current.

- 2. Based on the desired forced current, select an appropriate current range from Table 2.

- 3. Divide the desired forced current from step 1 by the current range from step 2 and multiply by 100 to calculate the Percent of Current Range Forced.

- 4. Based on the impedance of the load, calculate the voltage required to force the desired current from step 1. Use the following equation: **Voltage Required** =

#### Desired Current × Load Impedance.

- 5. Using Figure 5, locate the zone in which the Percent of Current Range Forced calculated in step 3 intersects with the voltage calculated in step 4. If the intersection is outside of Zone 1, then there are no warranted specifications. To get warranted specifications, the current range and/or forced current must be adjusted until the intersection is in Zone 1.

- 6. Based on the zone found in step 5, use <u>Table 2</u> to calculate the accuracy of the forced current.

| PPMU voltage clamps |                  |

|---------------------|------------------|

| Range               | -2 V to 6 V      |

| Resolution          | 122 μV           |

| Accuracy            | ±100 mV, typical |

#### **PPMU Measure Current**

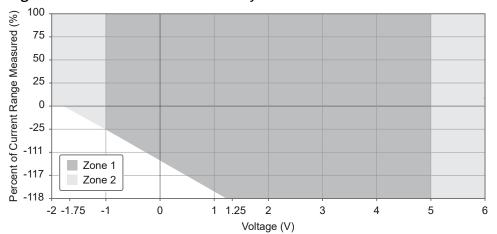

**Table 3. PPMU Measure Current Accuracy**

| Range   | Resolution | Accuracy                                                    |

|---------|------------|-------------------------------------------------------------|

| ±2 μA   | 460 pA     |                                                             |

| ±32 μA  | 7.3 nA     | ±1% of range for Zone 1 of<br>Figure 6, warranted           |

| ±128 μA | 30 nA      |                                                             |

| ±2 mA   | 460 nA     | ±1.5% of range for Zone 2 of<br><u>Figure 6</u> , warranted |

| ±32 mA  | 7.3 μΑ     |                                                             |

Figure 6. Warranted Current Accuracy Zones for PPMU Measure Current

**Note** The boundaries of Zone 1 are inclusive of that zone. All other boundaries are inclusive of Zone 2. The area outside of Zone 1 and Zone 2 does not have a warranted specification for PPMU measure current accuracy.

# **How to Calculate PPMU Measure Current Accuracy**

- 1. Specify the desired measured current.

- 2. Based on the desired measured current, select an appropriate current range from Table 3.

- 3. Divide the desired measured current from step 1 by the current range from step 2 and multiply by 100 to calculate the Percent of Current Range Measured.

- 4. If forcing voltage and then measuring current, Voltage in <u>Figure 6</u> is equal to the forced voltage. If forcing current and then measuring current, Voltage in <u>Figure 6</u> is equal to the voltage required to force the desired current based on the impedance of the load. Use the following equation: **Voltage Required = Desired Current** × **Load Impedance**.

- 5. Using <u>Figure 6</u>, locate the zone in which the Percent of Current Range Measured calculated in step 3 intersects with the Voltage calculated in step 4. If the intersection is outside of Zone 1 or Zone 2, then there are no warranted specifications. To get warranted specifications, the current range and forced current or forced voltage must be adjusted until the intersection is in Zone 1 or Zone 2.

- 6. Based on the zone found in step 5, use <u>Table 3</u> to calculate the accuracy of the measured current.

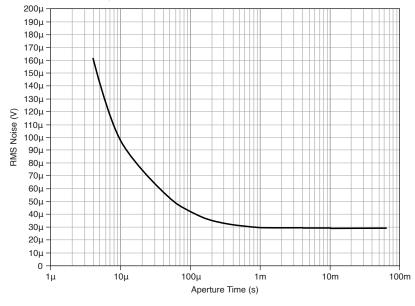

## **PPMU Programmable Aperture Time**

| Aperture time |       |  |

|---------------|-------|--|

| Minimum       | 4 μs  |  |

| Maximum       | 65 ms |  |

| Resolution    | 4 μs  |  |

Figure 7. Voltage Measurement Noise for Given Aperture Times, Typical

## **Opcodes**

Refer to the following table for supported opcodes. Using matched and failed opcode parameters with multiple PXIe-6571 instruments requires the PXIe-6674T synchronization module. Other uses of flow-control opcodes with multiple PXIe-6571 instruments only require NI-TClk synchronization.

| Category                      | Supported Opcodes                                                                                                                                                                                                     |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Flow Control                  | <ul> <li>repeat</li> <li>jump</li> <li>jump_if</li> <li>set_loop</li> <li>end_loop</li> <li>exit_loop</li> <li>exit_loop_if</li> <li>call</li> <li>return</li> <li>keep_alive</li> <li>match</li> <li>halt</li> </ul> |

| Sequencer Flags and Registers | <ul><li>set_seqflag</li><li>clear_seqflag</li><li>write_reg</li></ul>                                                                                                                                                 |

| Signal                        | <ul><li>set_signal</li><li>pulse_signal</li><li>clear_signal</li></ul>                                                                                                                                                |

| Digital Source and Capture    | <ul><li>capture_start</li><li>capture</li><li>capture_stop</li><li>source_start</li><li>source</li><li>sourced_replace</li></ul>                                                                                      |

# **Pipeline Latencies**

| Minimum delay between source_start opcode and the first source opcode or subsequent source_start opcode | 3 μs |  |

|---------------------------------------------------------------------------------------------------------|------|--|

|                                                                                                         |      |  |

| Matched and failed condition pipeline latency | 80 cycles |

|-----------------------------------------------|-----------|

|-----------------------------------------------|-----------|

# **Source and Capture**

| Digital Source <sup>11[11]</sup> |                                                |

|----------------------------------|------------------------------------------------|

| Operation modes                  | Serial and parallel; broadcast and site-unique |

| Source memory size               | 32 MB (256 Mbit) total                         |

| Maximum waveforms                | 512                                            |

| Digital Capture <sup>[11]</sup> |                                  |  |

|---------------------------------|----------------------------------|--|

| Operation modes                 | Serial and parallel; site-unique |  |

| Capture memory size             | 1 million samples                |  |

| Maximum waveforms               | 512                              |  |

## **Independent Clock Generators**

| Number of clock generators |                 |

|----------------------------|-----------------|

| PXIe-6571 (8-channel)      | 8 (one per pin) |

11. To learn how to calculate achievable data rates for Digital Source or Digital Capture, visit ni.com/info and enter the Info Code DigitalSourceCapture to access the Calculating Digital Source Rate tutorial or the Calculating Digital Capture Rate tutorial.

| PXIe-6571 (32-channel) | 32 (one per pin) |

|------------------------|------------------|

|------------------------|------------------|

| Clock period range      | 6.25 ns to 40 us (160 MHz to 25 kHz) <sup>12</sup> |

|-------------------------|----------------------------------------------------|

| Clock period resolution | 38 fs                                              |

## **Frequency Measurements**

| Frequency counter measure frequency |                                                |

|-------------------------------------|------------------------------------------------|

| Range                               | 5 kHz to 200 MHz, 2.5 ns minimum pulse width   |

| Accuracy                            | See <u>Calculating Frequency Counter Error</u> |

### **Calculating Frequency Counter Error**

Use the following equation to calculate the frequency counter error (ppm).

$$\left| \frac{\mathit{TB}_{err}}{\left( 1 - \mathit{TB}_{err} \right)} + \frac{20 \, \mathrm{ns}}{\left( \mathit{Measurement Time - Unknown Clock Period} \right)} \right| \times 1, \, 000, \, 000$$

#### where

- *Measurement Time* is the time, in seconds, over which the frequency counter measurement is configured to run

- *Unknown Clock Period* is the time, in seconds, of the period of the signal being measured

- TBerr is the error of the Clk100 timebase

- 12. Clocks with *Period* < 7.5 ns will have a non-50% duty cycle.

Refer to the following table for a few examples of common Clk100 timebase accuracies.

Table 4. TBerr

| PXI Express Hardware<br>Specification Revision 1.0 | PXIe-1095 Chassis | PXIe-6674T Override |

|----------------------------------------------------|-------------------|---------------------|

| 100 μ (100 ppm)                                    | 25 μ (25 ppm)     | 80 n (80 ppb)       |

# Example 1: Calculating Error with a PXIe-1095 Chassis

Calculate the error of performing a frequency measurement of a 10 MHz clock (100 ns period) with a 1 ms measurement time using the PXIe-Clk100 provided by the PXIe-1095 chassis as the timebase.

#### Solution

$$\left(\frac{25\mu}{(1-25\mu)} + \frac{20ns}{(1ms-100ns)}\right) \times 1$$

, 000, 000 = 45 ppm

# Example 2: Calculating Error when Overriding with the PXIe-6674T

Calculate the error if you override the PXIe-Clk100 timebase with the PXIe-6674T and increase the measurement time to 10 ms.

#### Solution

$$\left(\frac{80n}{(1-80n)} + \frac{20ns}{(10ms-100ns)}\right) \times 1$$

, 000, 000 = 2 ppm

## **Calibration Interval**

| d calibration interval 1 year |

|-------------------------------|

|-------------------------------|

## **Safety Voltages**

Connect only voltages that are within these limits.

| Supported measurement range <sup>13</sup> | -2 V to 7 V <sup>14</sup> |

|-------------------------------------------|---------------------------|

| Measurement Category                      | CAT I                     |

## **Measurement Category**

**Caution** Do not connect the product to signals or use for measurements within Measurement Categories II, III, or IV.

Measurement Category I is for measurements performed on circuits not directly connected to the electrical distribution system referred to as **MAINS** voltage. MAINS is a hazardous live electrical supply system that powers equipment. This category is for measurements of voltages from specially protected secondary circuits. Such voltage measurements include signal levels, special equipment, limited-energy parts of equipment, circuits powered by regulated low-voltage sources, and electronics.

**Note** Measurement Categories CAT I and CAT O are equivalent. These test and measurement circuits are for other circuits not intended for direct connection to the MAINS building installations of Measurement Categories CAT II, CAT III, or CAT IV.

#### **Environmental Guidelines**

**Notice** This model is intended for use in indoor applications only.

- 13. If the total voltage sourced or driven on any pin relative to GND exceeds the supported measurement range, instrument performance may be degraded.

- 14. *Voltage* > 6 V requires the Extended Voltage Range mode of operation.

## **Environmental Characteristics**

| Temperature             |                 |

|-------------------------|-----------------|

| Operating <sup>15</sup> | 0 °C to 40 °C   |

| Storage                 | -40 °C to 71 °C |

| Humidity  |                           |

|-----------|---------------------------|

| Operating | 10% to 90%, noncondensing |

| Storage   | 5% to 95%, noncondensing  |

| Pollution Degree | 2                                                 |

|------------------|---------------------------------------------------|

| Maximum altitude | 2,000 m (800 mbar) (at 25 °C ambient temperature) |

| Shock and Vibration     |                              |

|-------------------------|------------------------------|

| Operating vibration     | 5 Hz to 500 Hz, 0.3 g RMS    |

| Non-operating vibration | 5 Hz to 500 Hz, 2.4 g RMS    |

| Operating shock         | 30 g, half-sine, 11 ms pulse |

<sup>15.</sup> The PXIe-6571 (8-channel) requires a chassis with ≥58 W slot cooling capacity; the PXIe-6571 (32-channel) requires a chassis with 82 W slot cooling capacity. Refer to the specifications for your PXI chassis to determine the ambient temperature ranges your chassis can achieve.

# **Physical Characteristics**

| PXIe slots | 1                                                        |

|------------|----------------------------------------------------------|

| Dimensions | 131 mm × 21 mm × 214 mm (5.16 in. × 0.83 in. × 8.43 in.) |

| Weight     | 640 g (22.5 oz.)                                         |

#### **Related information:**

• <u>Dimensional Drawings</u>

## **Power Requirements**

The PXIe-6571 draws current from a combination of the 3.3 V and 12 V power rails. The maximum current drawn from each of these rails can vary depending on the PXIe-6571 mode of operation.

| Input power            |      |

|------------------------|------|

| PXIe-6571 (8-channel)  | 49 W |

| PXIe-6571 (32-channel) | 76 W |

| Current draw, PXIe-6571 (8-channel) |       |

|-------------------------------------|-------|

| 3.3 V                               | 1.3 A |

| 12 V                                | 3.7 A |

| Current draw, PXIe-6571 (32-channel) |       |

|--------------------------------------|-------|

| 3.3 V                                | 1.7 A |

| 12 V                                 | 5.9 A |